简介

这是学习SDSoc的第二个入门实验,通过EMIO点亮连接在PL上的8个LED。与上一个实验不一样,在这一个实验中,由于ZedBoard平台中没有使能EMIO,因此想直接通过SDSoc编写程序驱动MIO是不行的,所以这一个实验需要自己搭建包含EMIO的平台。

我用的是ZedBoard开发板,SDSoc2017.4。

第一步:搭建平台

通过对官方资料的学习,平台分为软件平台和硬件平台两部分,官方就如何搭建平台提供了较为详细的说明,可以在XILINX官网中搜索ug1146 和ug1236 两篇文档并下载。其中ug1146 理论讲解比较详细,ug1236 重在叙述操作实践,本实验需要搭建的平台就是参照这两篇文档,同时增加了一点点东西完成的。

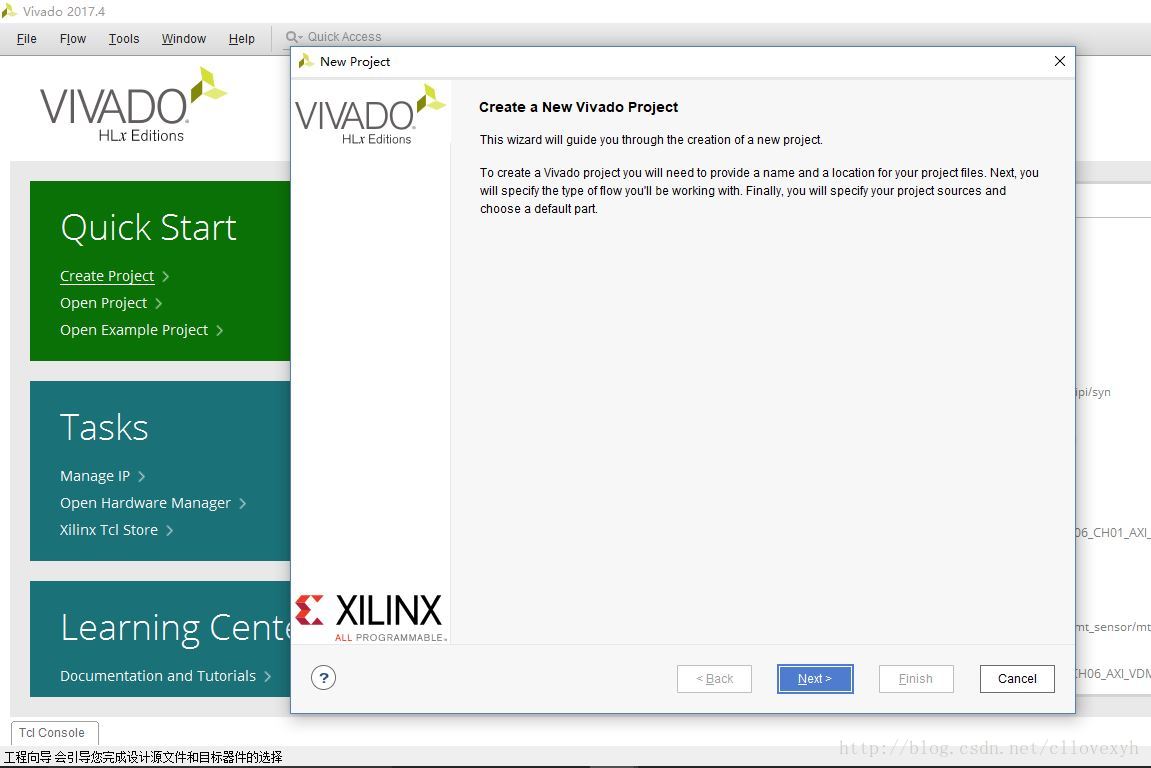

1、新建VIVADO工程,点击Next;

2、设置工程名和路径,这里设置为zedemio,点击Next;

3、选择RTL工程,点击Next;

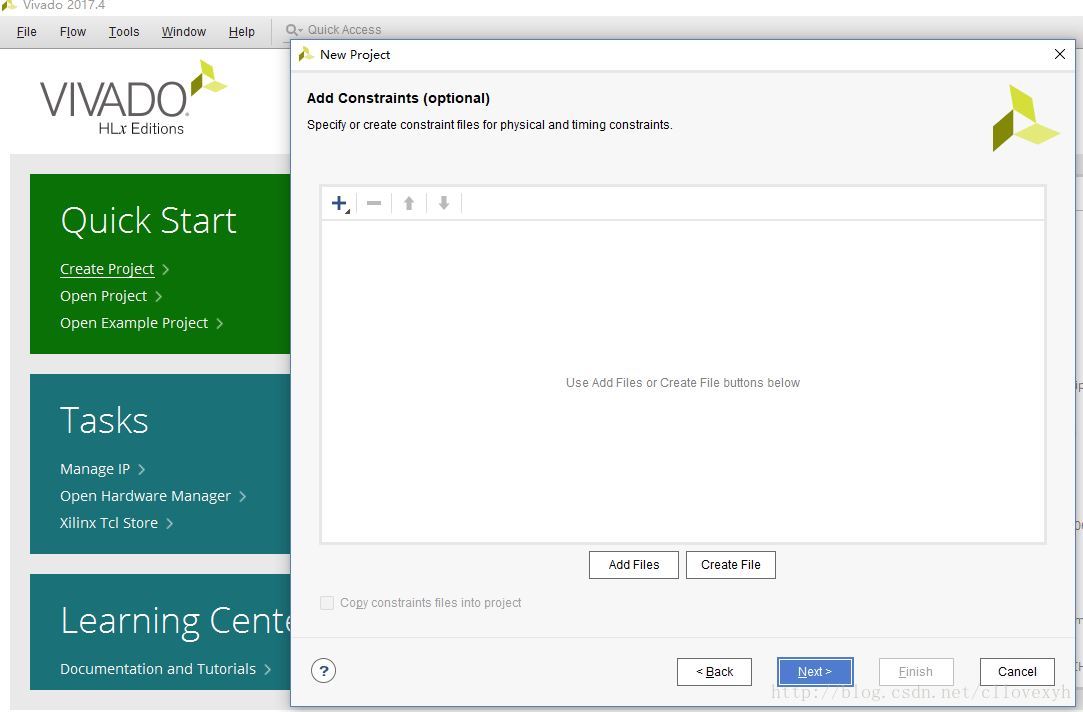

4、源文件和约束文件设置,直接Next;

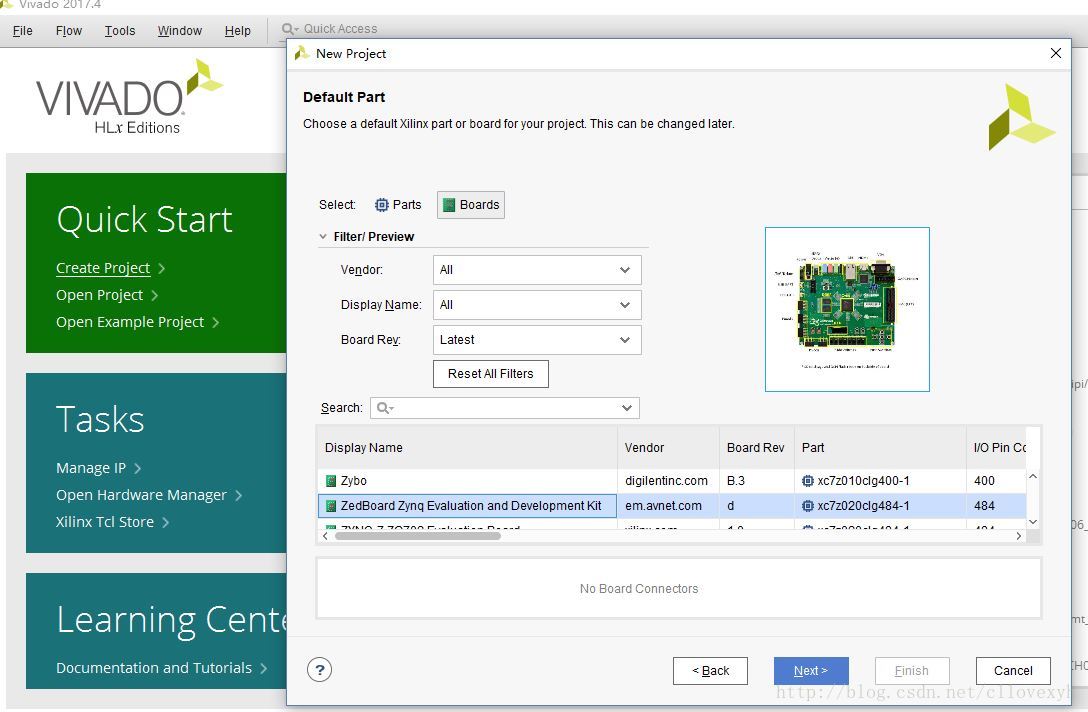

5、因为用的是ZedBoard开发板,所以在Boards中选择ZedBoard即可,点击Next,然后Finish。

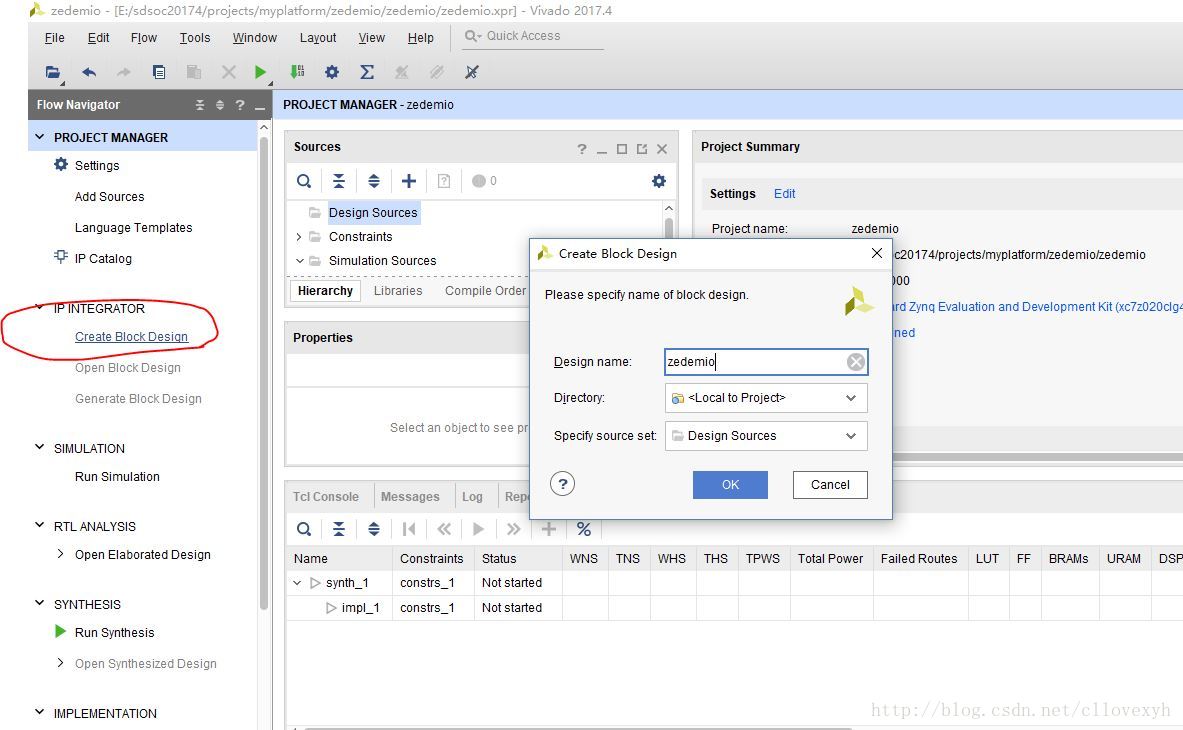

6、点击红圈所示的Create Block Design,在弹出的界面中设置Design name,注意这里设置的名字一定要和工程名一样,否则搭建的平台在运行时会报错(亲自试验过),这个要求在ug1146 中也有说明。

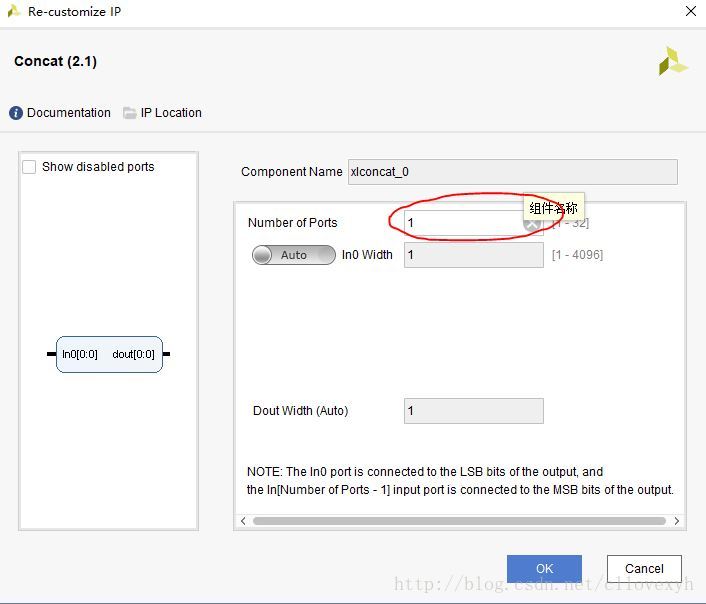

ug1146 第28页

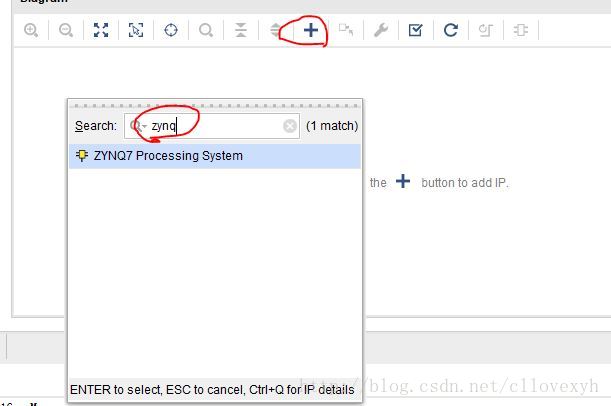

7、点击‘+’,搜索zynq,双击ZYNQ7 Processing System

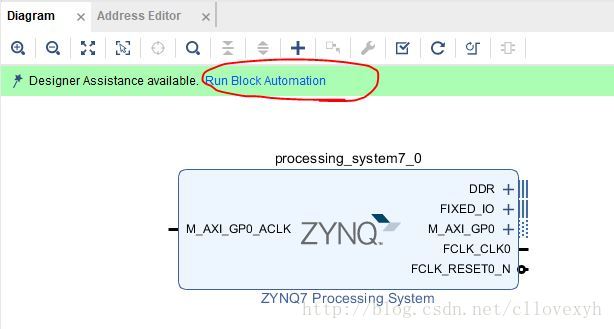

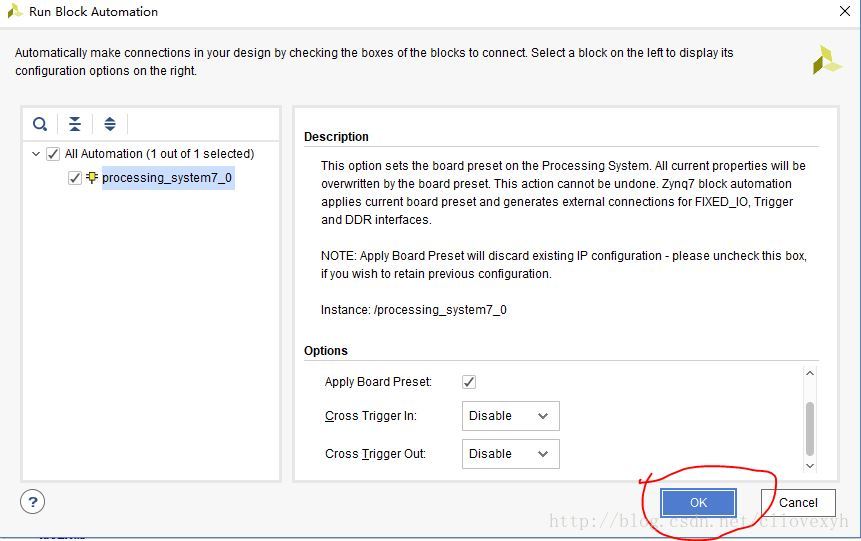

8、点击Run Block Automation->OK

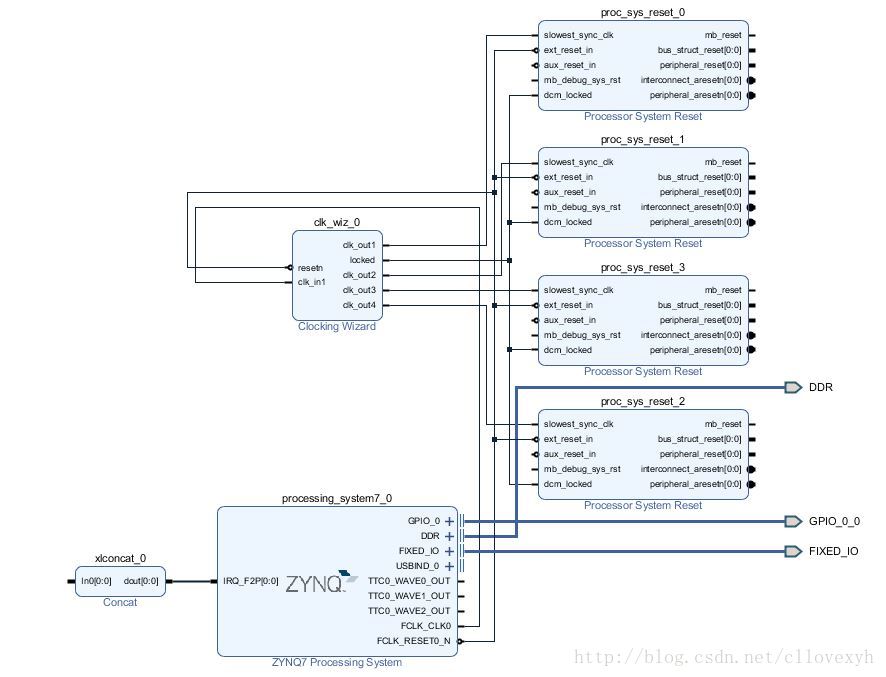

9、然后继续添加IP,如图所示

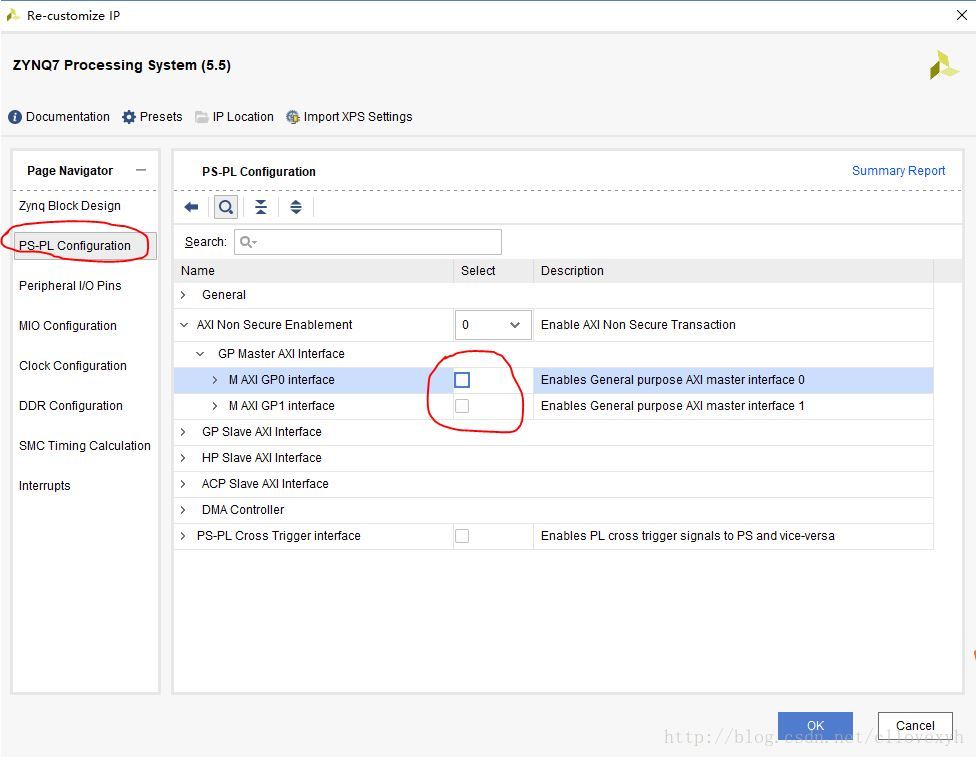

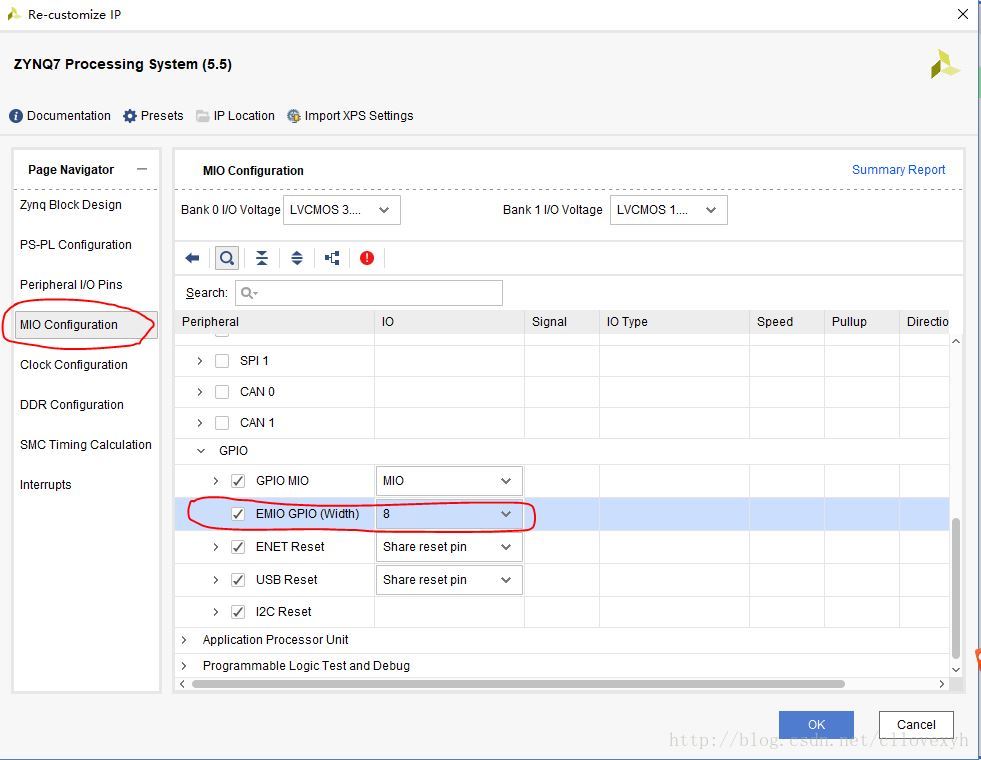

10、双击ZYNQ7 Processing System进行如下配置,然后点击OK

添加8个EMIO,因为有开发板上有8个LED。

添加PL到PS中断。

11、双击Concat进行如下配置,然后点击OK

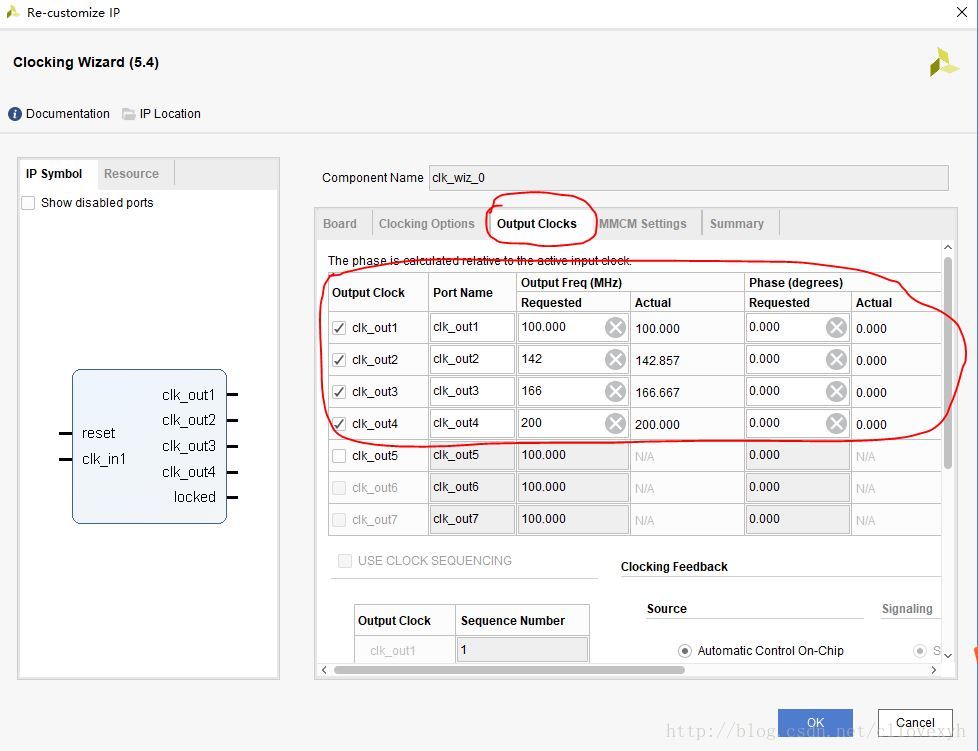

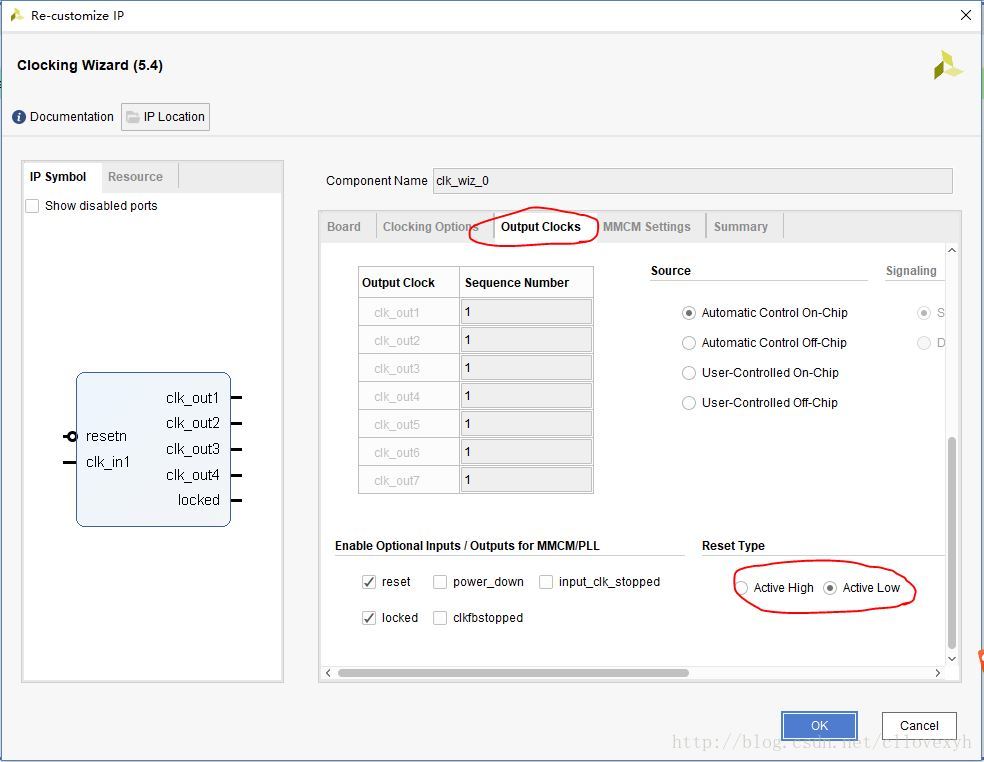

12、双击Clocking Wizard进行如下配置,然后点击OK

13、配置结束后就将框图连接成如下图

14、点击Validate Design,直到出现正确弹框,点击OK,然后Ctrl+s保存。

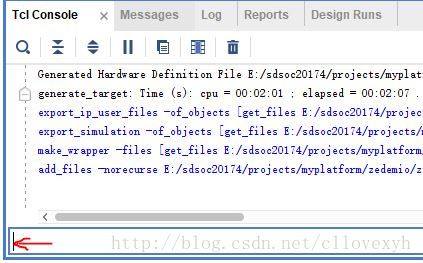

15、接下来就需要在箭头所指位置输入Tcl命令了

set_property PFM_NAME "xilinx.com:zedemio:zedemio:1.0" [get_files E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.bd]

回车,E:/xxxxxx/zedemio.bd路径是这个工程产生bd文件的路径,在这个路径下可以找到这个工程的bd文件。

set_property PFM.CLOCK { \

clk_out1 {id "0" is_default "true" proc_sys_reset "proc_sys_reset_0" } \

clk_out2 {id "1" is_default "false" proc_sys_reset "proc_sys_reset_1" } \

clk_out3 {id "2" is_default "false" proc_sys_reset "proc_sys_reset_2" } \

clk_out4 {id "3" is_default "false" proc_sys_reset "proc_sys_reset_3" } \

} [get_bd_cells /clk_wiz_0]

set_property PFM.AXI_PORT { \

M_AXI_GP0 {memport "M_AXI_GP"} \

M_AXI_GP1 {memport "M_AXI_GP"} \

S_AXI_ACP {memport "S_AXI_ACP" sptag "ACP" memory "processing_system7_0

ACP_DDR_LOWOCM"} \

S_AXI_HP0 {memport "S_AXI_HP" sptag "HP0" memory "processing_system7_0

HP0_DDR_LOWOCM"} \

S_AXI_HP1 {memport "S_AXI_HP" sptag "HP1" memory "processing_system7_0

HP1_DDR_LOWOCM"} \

S_AXI_HP2 {memport "S_AXI_HP" sptag "HP2" memory "processing_system7_0

HP2_DDR_LOWOCM"} \

S_AXI_HP3 {memport "S_AXI_HP" sptag "HP3" memory "processing_system7_0

HP3_DDR_LOWOCM"} \

} [get_bd_cells /processing_system7_0]

set intVar []

for {set i 0} {$i < 16} {incr i} {

lappend intVar In$i {}

}

set_property PFM.IRQ $intVar [get_bd_cells /xlconcat_0]

回车,这些语句在ug1236 中都有详细的说明。

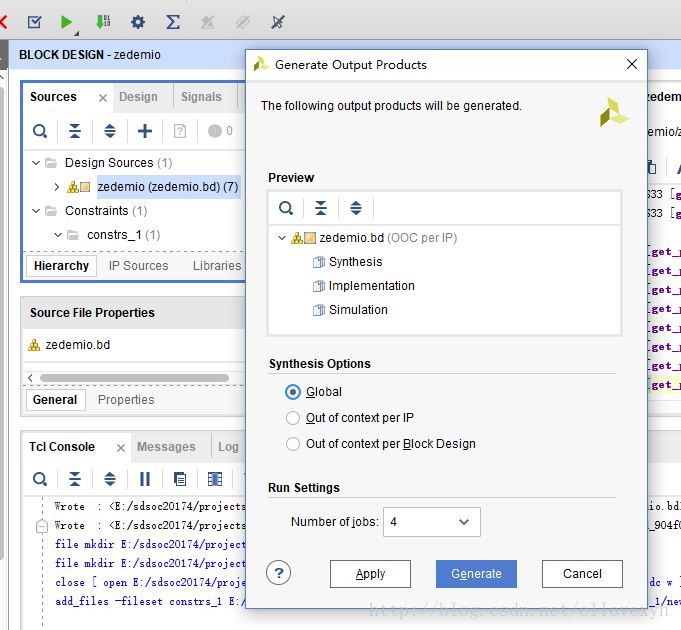

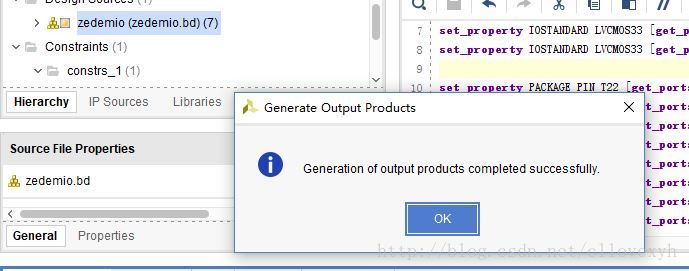

16、右击zedemio->Generate Output Products->选择Global->点击Generate

完成后点击OK

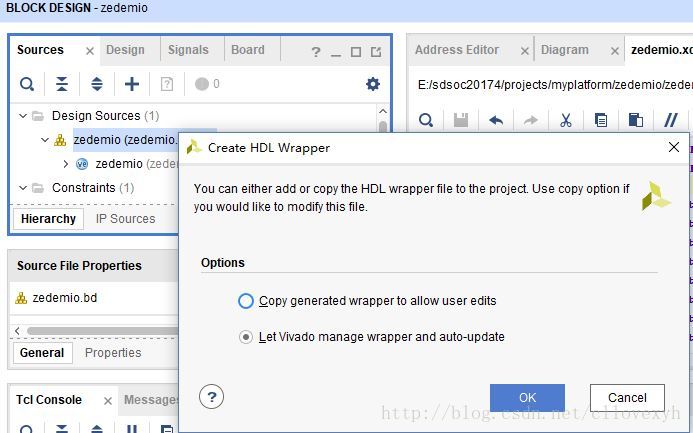

17、右击zedemio->Generate HDL Wrapper->选择auto-updata->点击OK

18、由于我们这里要点亮连接在PL上8个LED,所有需要对这些LED进行约束。

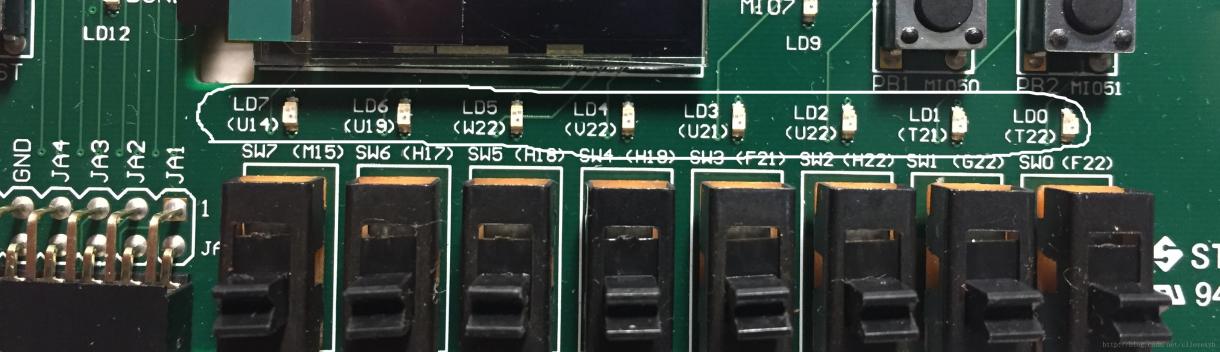

1、8个LED连接在PL上的引脚位置,如图,这8个LED分别是LD0~LD7,引脚位置分别为:T22、T21、U22、U21、V22、W22、U19、U14。

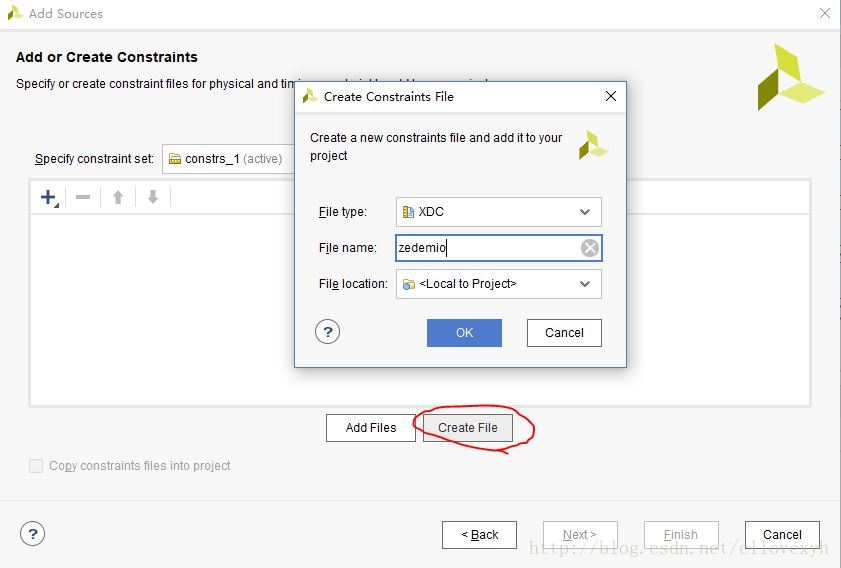

2、创建约束文件,右击Constrains->Add Sources

点击Next;

点击Create File,File name设置为zedemio,点击OK->点击Finish。

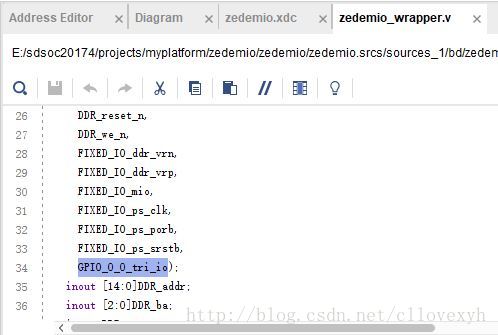

3、添加约束文件

约束文件要参照顶层文件中的接口名字进行添加

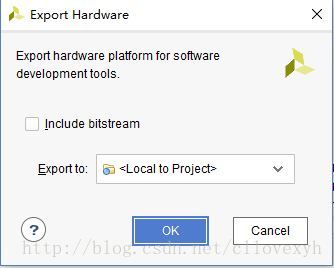

19、导出硬件,点击OK

20、输入Tcl语句,生成.dsa文件

write_dsa -force E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.dsa

将zedemio.dsa文件生成在Tcl语句中指定的路径下

validate_dsa E:/sdsoc20174/projects/myplatform/zedemio/zedemio/zedemio.srcs/sources_1/bd/zedemio/zedemio.dsa

这样,硬件平台就搭建完成了,接着就是搭建软件平台。

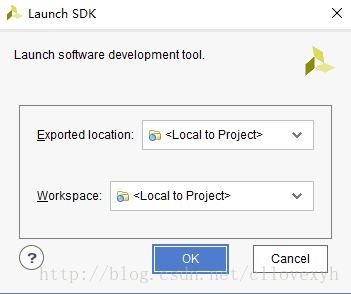

21、在当前VIVADO工程中加载SDK(方便一些),点击OK

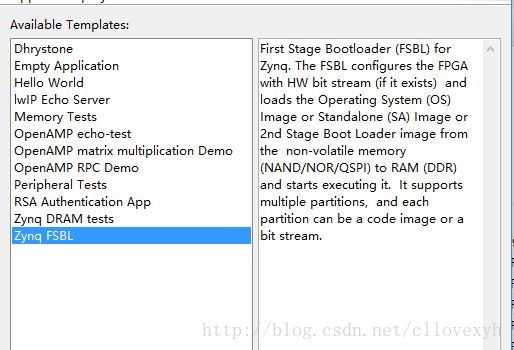

新建一个fsbl文件,点击Next;

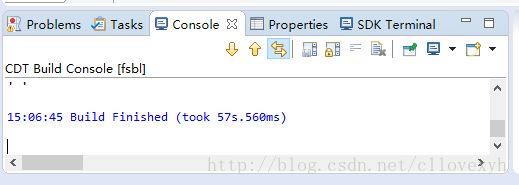

选择Zynq FSBL,然后点击Finish,等待创建完成。

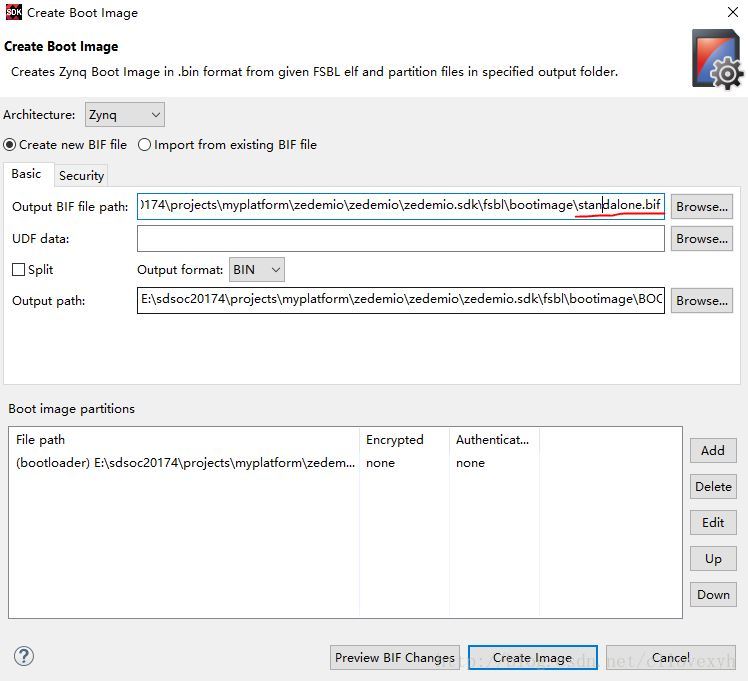

右击fsbl文件夹->Create Boot Image;修改.bif文件名,点击Create Image;

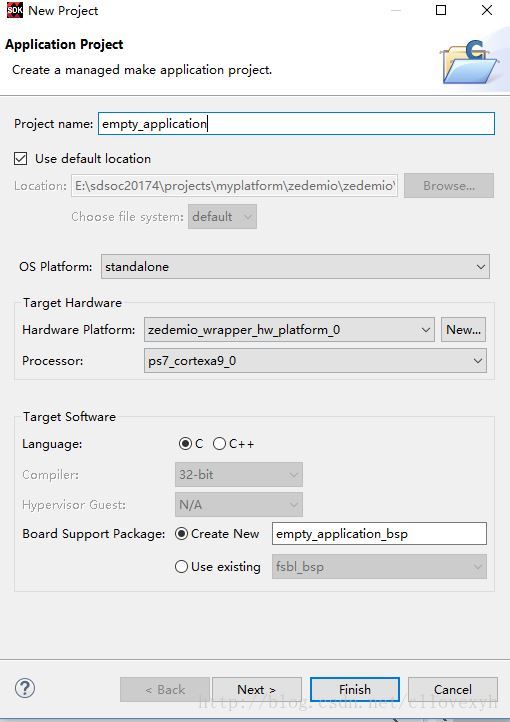

因为在SDx中,平台创建过程需要一个新的链接器脚本。这个链接器脚本基本上确保了针对自定义平台的任何应用程序代码,驻留并运行在执行板上的DDR内存中。要创建一个新的链接器脚本,我们将创建一个空应用程序。

点击Finish,等待创建完成;

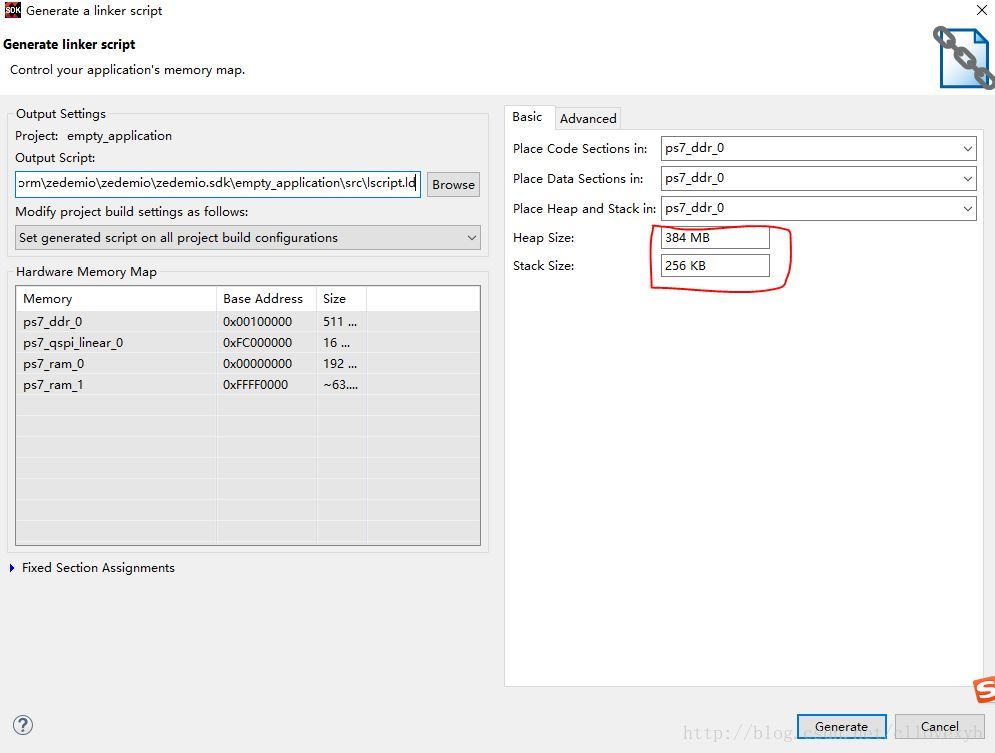

完成后右击empty_application文件夹->Generate Linker Script,在Heap Size中输入402653184(384M);在Stack Size中输入262144(256K);点击Generate。

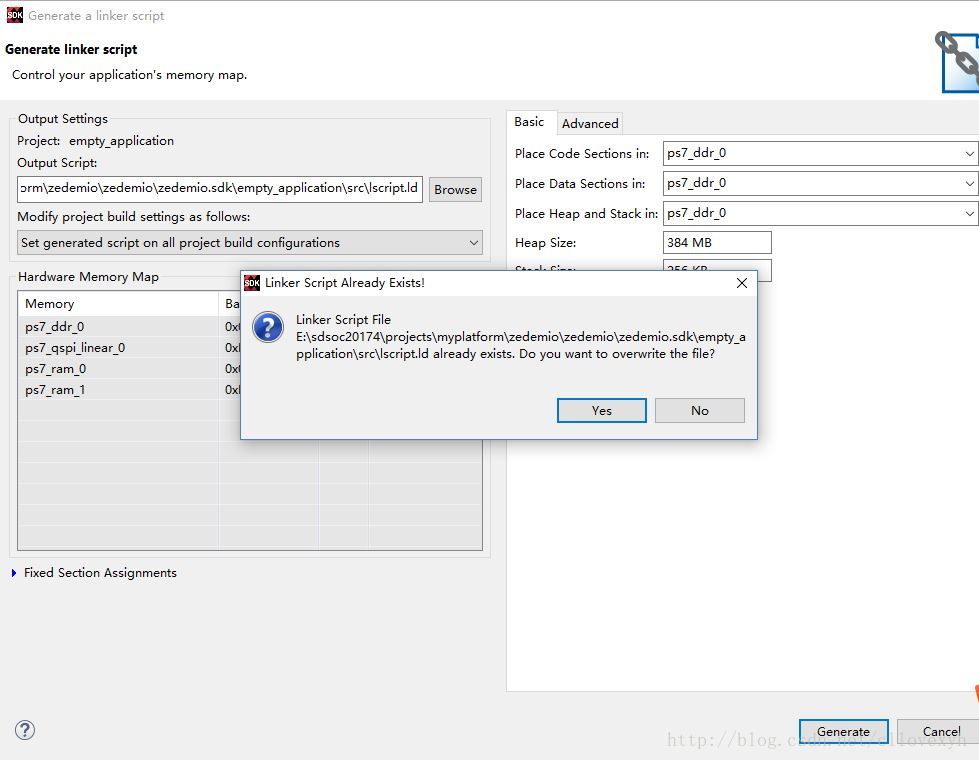

点击Yes即可,之后就可以关闭SDK了。

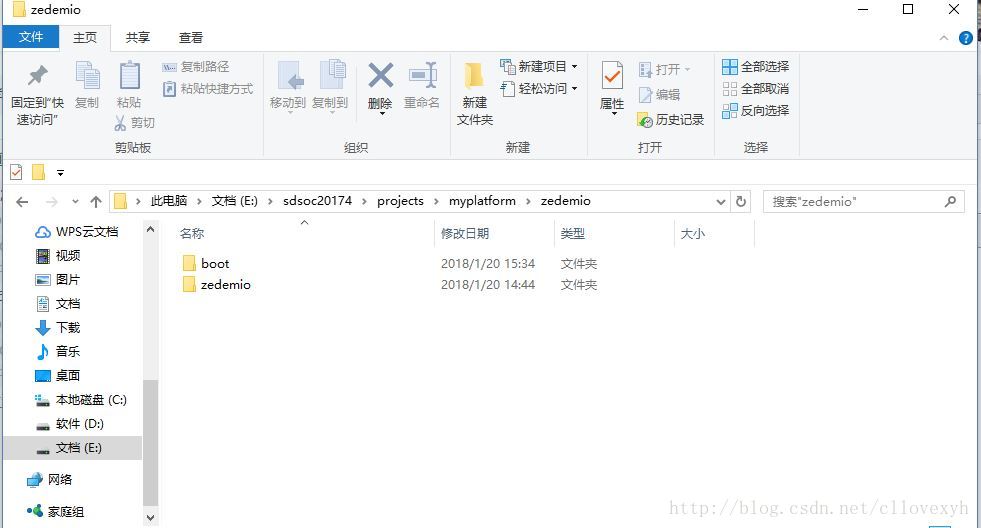

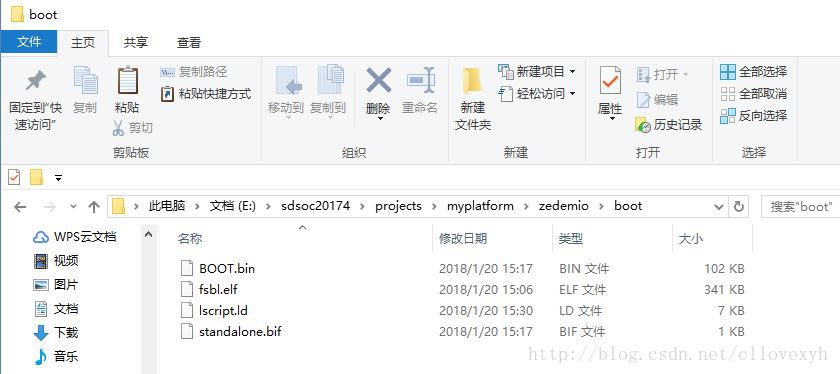

然后在工程文件夹的位置新建一个名为boot的文件夹

将

BOOT.bin(E:\sdsoc20174\projects\myplatform\zedemio\zedemio\zedemio.sdk\fsbl\bootimage);

standalone.bif(E:\sdsoc20174\projects\myplatform\zedemio\zedemio\zedemio.sdk\fsbl\bootimage);

fsbl.elf(E:\sdsoc20174\projects\myplatform\zedemio\zedemio\zedemio.sdk\fsbl\Debug);

lscript.ld(E:\sdsoc20174\projects\myplatform\zedemio\zedemio\zedemio.sdk\empty_application\src)

这4个文件复制到新建的那个boot文件夹里。

打开standalone.bif文件,将其修改成下图所示,然后ctrl+s保存。

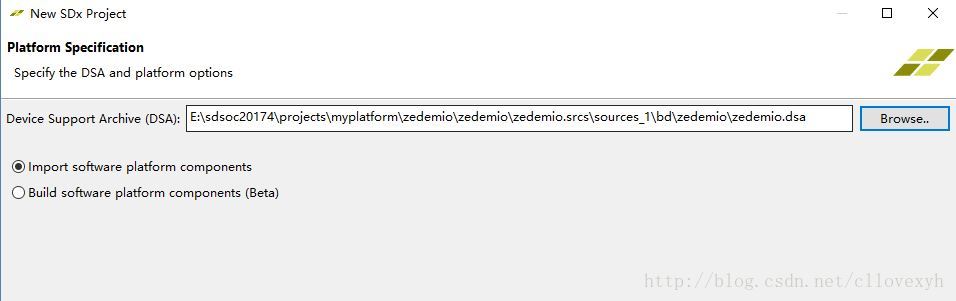

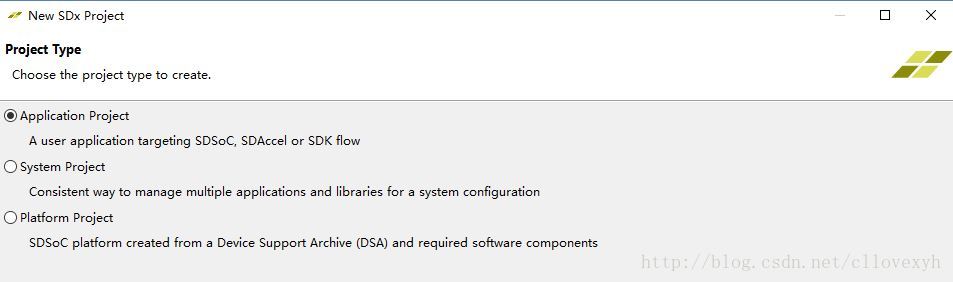

22、打开SDSoc,新建一个Platform Project,点击Next;

定位到硬件平台生成的zedemio.dsa文件,选择导入软件平台成分,点击Finish。

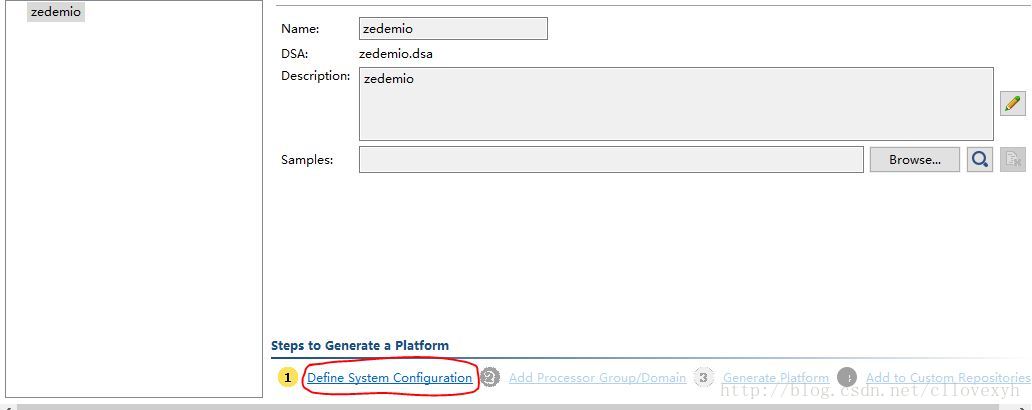

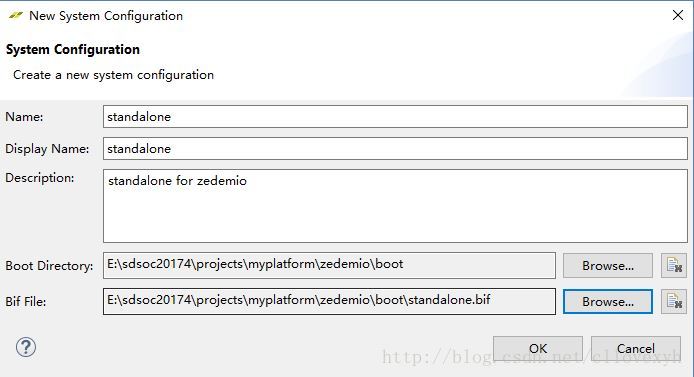

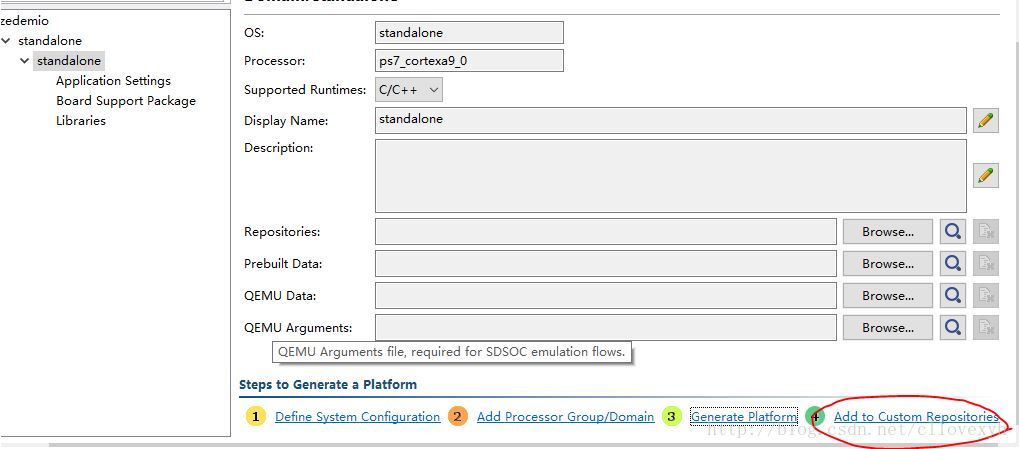

点击Define System Configuration;

在接下来的弹框中填入以下信息,Name和Display Name表示系统的名字,这里叫standalone(裸机);Description随便写吧;Boot Dictionary就是前面新建的boot文件夹;Bif File就是在boot文件夹中的standaalone.bif文件;点击OK。

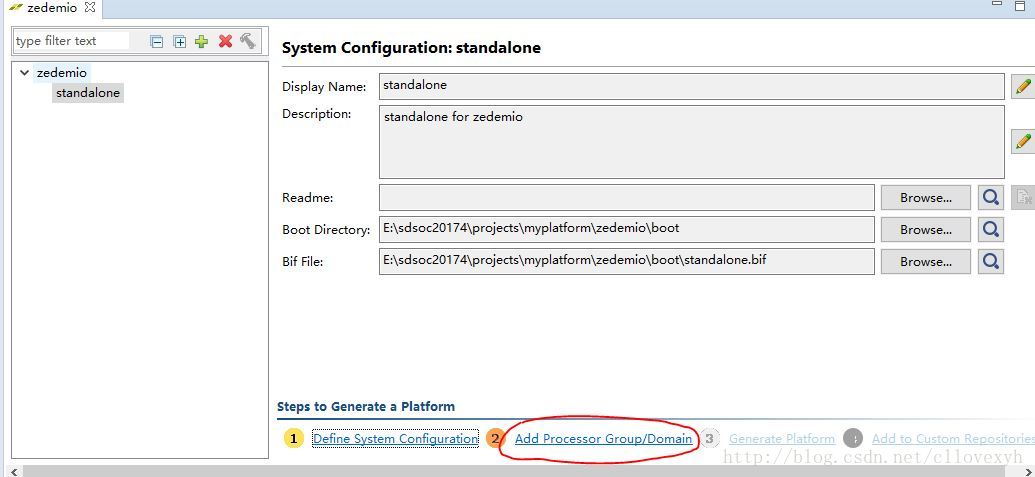

点击Add Processor Group/Domain;

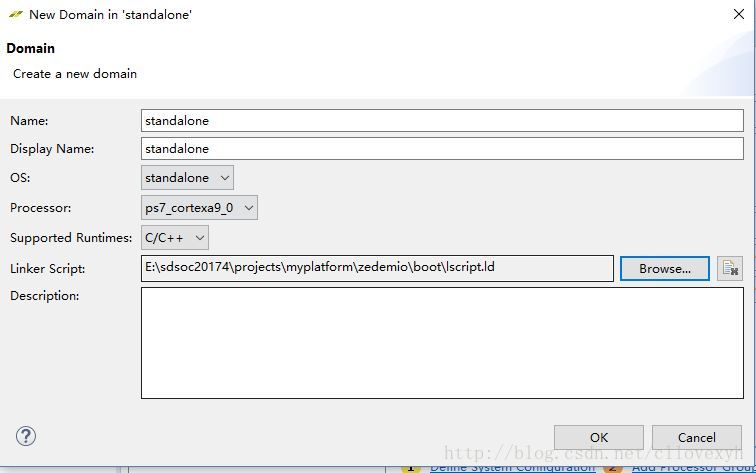

在接下来的弹框中填入以下信息,其中Name和Display Name就是系统的名字,OS选择standalone(裸机),Linker Script选择boot文件夹中的lscript.ld;点击OK。

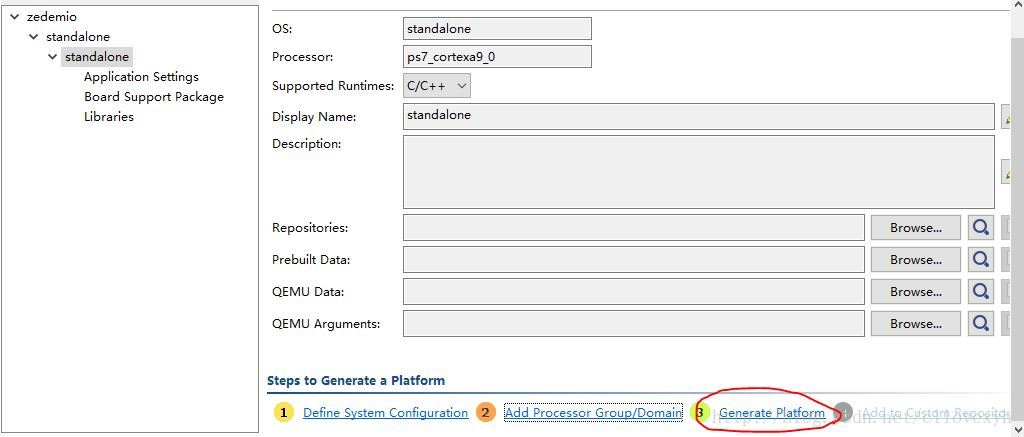

接着点击Generate Platform产生平台;

弹框表示已经产生一个名为zedemio的平台,点击OK;

接着点击Add to Custom Repositories,添加这个平台;

已经添加这个名为zedemio的平台,点击OK。

至此,我们就搭建了一个名为zedemio的平台了,下面测试一下这个平台。

第二步:测试平台

1、新建一个SDSoc Application Project,点击Next;

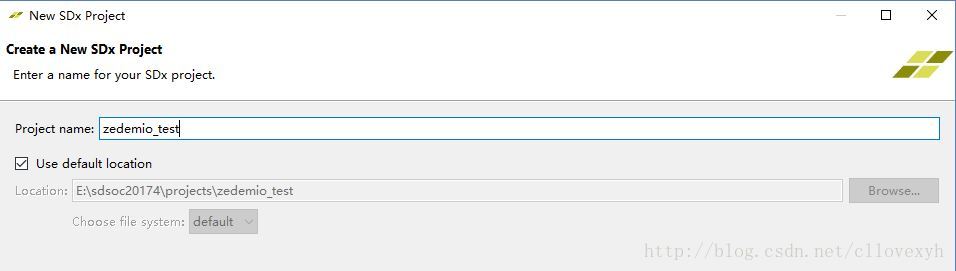

2、命名为zedemio_test,点击Next;

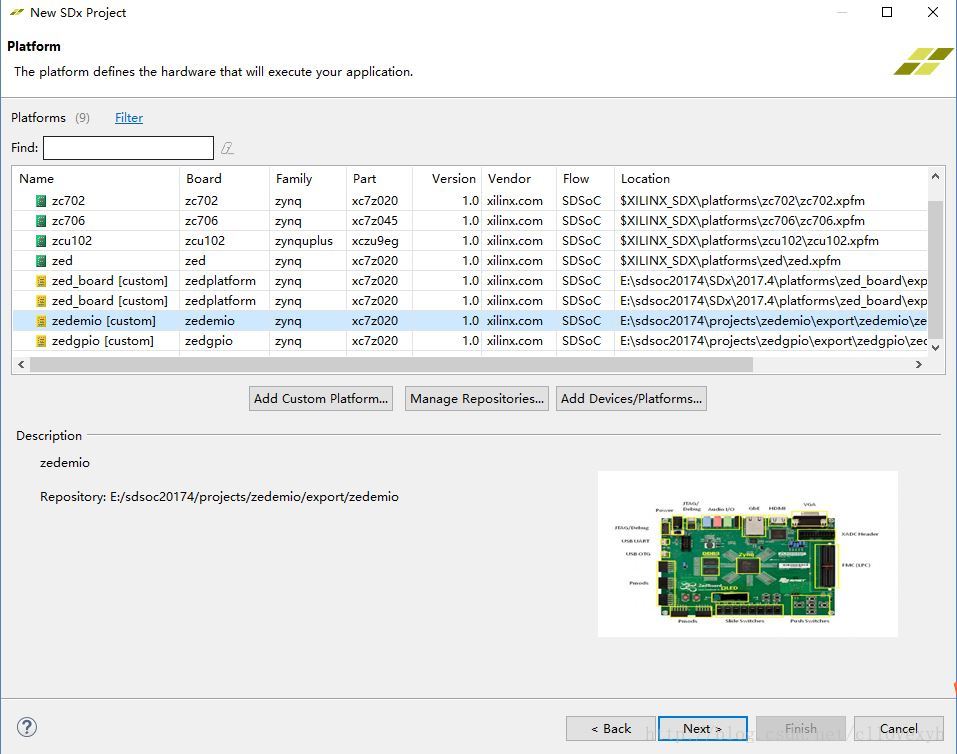

3、在接下来的选择平台界面,就出现了刚才创建的zedemio这个平台,选择这个平台,点击Next;

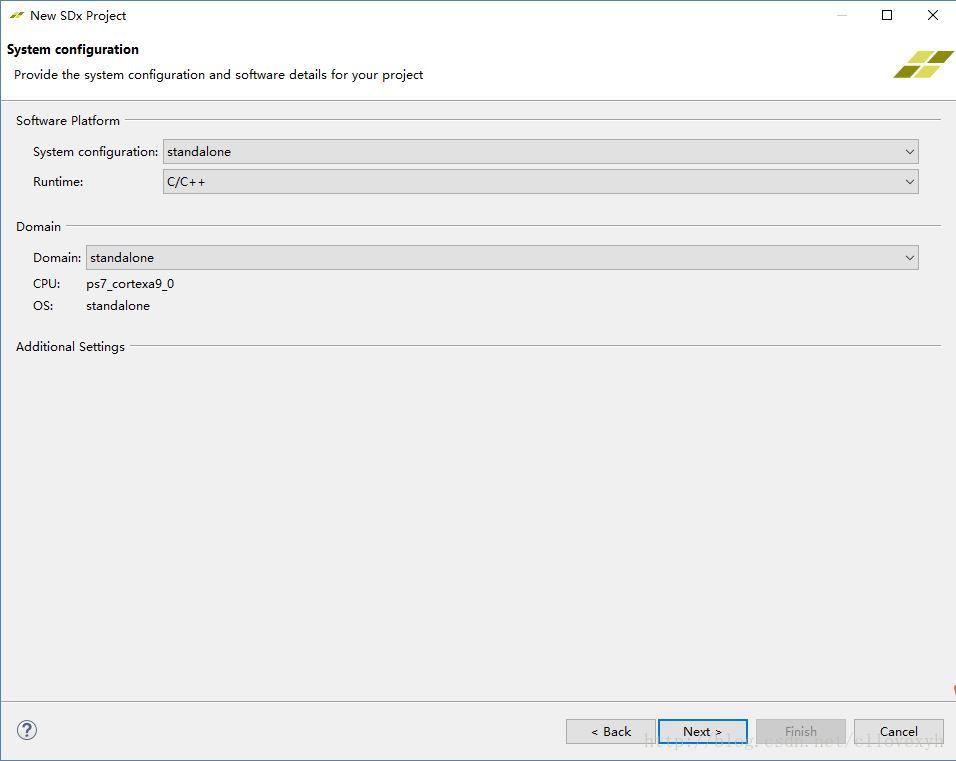

4、接着选择系统配置,由于只添加了standalone,所有只有standalone可选,点击Next;

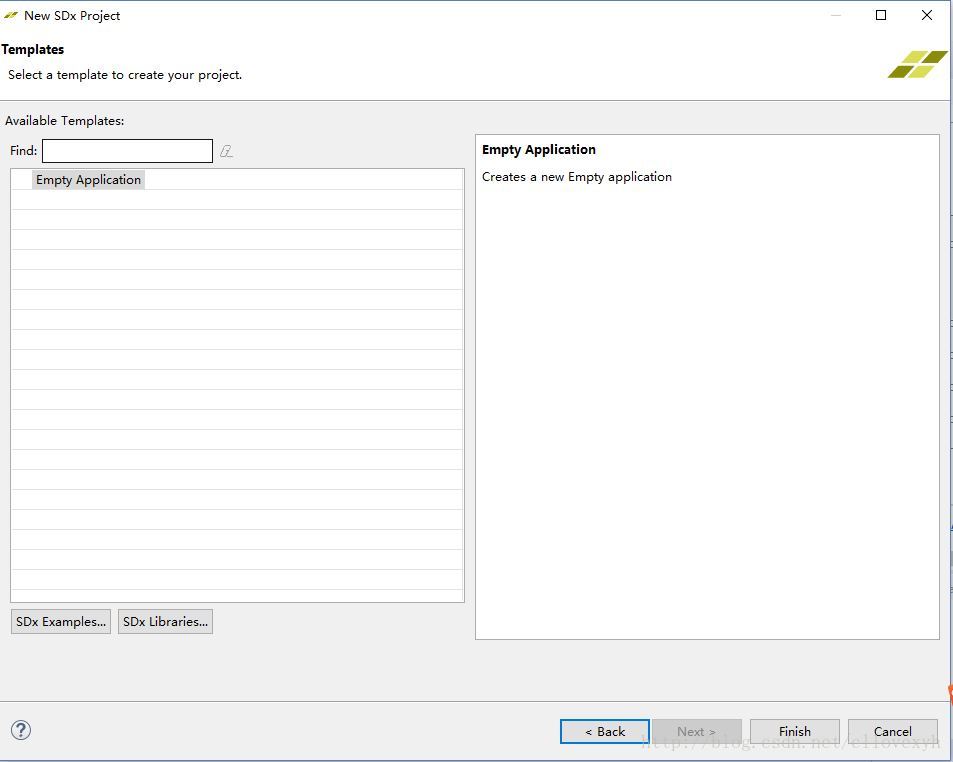

5、由于没有添加例程,只有选择创建一个Empty Application;点击Finish。

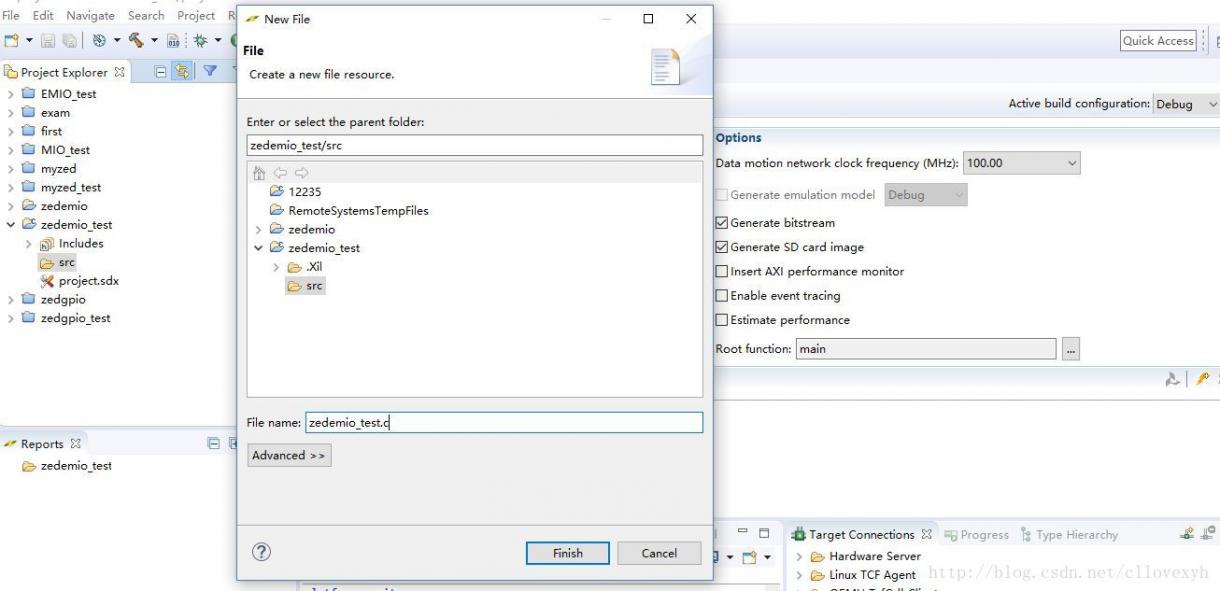

6、之后的操作就SDSoc学习(一) 中一样了,选择Debug、Generate SD Image,然后新建一个zedemio_test.c文件

在zedemio_test.c中写入如下代码

#include "xgpiops.h"

#include "sleep.h"

int main() {

static XGpioPs psGpioInstancePtr;

XGpioPs_Config* GpioConfigPtr;

int xStatus;

//--EMIO的初始化

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

if (GpioConfigPtr == NULL)

return XST_FAILURE;

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr, GpioConfigPtr,

GpioConfigPtr->BaseAddr);

if (XST_SUCCESS != xStatus)

print("PS GPIO INIT FAILED \n\r");

//--EMIO的输入输出操作

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 54, 1); //配置EMIO输出方向,0输入1输出

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 54, 1); //配置EMIO的第54位输出,0输入1输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 55, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 55, 1); //配置EMIO的第55位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 56, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 56, 1); //配置EMIO的第56位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 57, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 57, 1); //配置EMIO的第57位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 58, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 58, 1); //配置EMIO的第57位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 59, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 59, 1); //配置EMIO的第57位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr,60, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 60, 1); //配置EMIO的第57位输出

XGpioPs_SetDirectionPin(&psGpioInstancePtr, 61, 1); //配置EMIO输出方向

XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 61, 1); //配置EMIO的第57位输出

while (1) {

XGpioPs_WritePin(&psGpioInstancePtr, 54, 1); //点亮EMIO的第54位输出1

usleep(500000); //延时,单位us

XGpioPs_WritePin(&psGpioInstancePtr, 54, 0); //EMIO的第54位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 55, 1); //EMIO的第55位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 55, 0); //EMIO的第55位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 56, 1); //EMIO的第56位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 56, 0); //EMIO的第56位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 57, 1); //EMIO的第57位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 57, 0); //EMIO的第57位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 58, 1); //点亮EMIO的第54位输出1

usleep(500000); //延时,单位us

XGpioPs_WritePin(&psGpioInstancePtr, 58, 0); //EMIO的第54位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 59, 1); //EMIO的第55位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 59, 0); //EMIO的第55位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 60, 1); //EMIO的第56位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 60, 0); //EMIO的第56位输出0

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 61, 1); //EMIO的第57位输出1

usleep(500000); //延时

XGpioPs_WritePin(&psGpioInstancePtr, 61, 0); //EMIO的第57位输出0

usleep(500000); //延时

}

return 0;

}

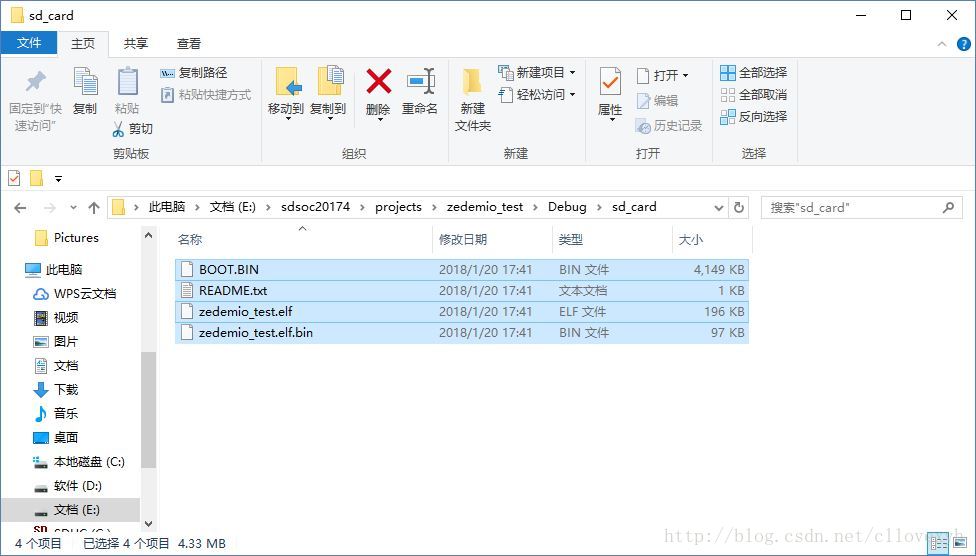

然后选择Build Debug,然后等待完成即可(这个时间有些长);Debug完成之后,将sd_card中的四个文件拷贝到SD卡中,然后给开发板上电后就可看到流水灯现象了。

结束

这个实验通过搭建一个简单的平台,将搭建平台的流程走了一遍,争取下一次搭建一个包含其他IP控制外设的平台,其实这个流程在官方资料ug1146 和ug1236 上有更加详细的解释和说明,在XILINX官网上很容易搜索到,这里就不上传了。对于这个流程如有疑问,还请查阅官方资料,当然也欢迎留言交流。

本文转载自:CLGo的博客

*本文由作者授权转发,如需转载请联系作者本人