作者:OpenSLee;来源:FPGA开源工作室

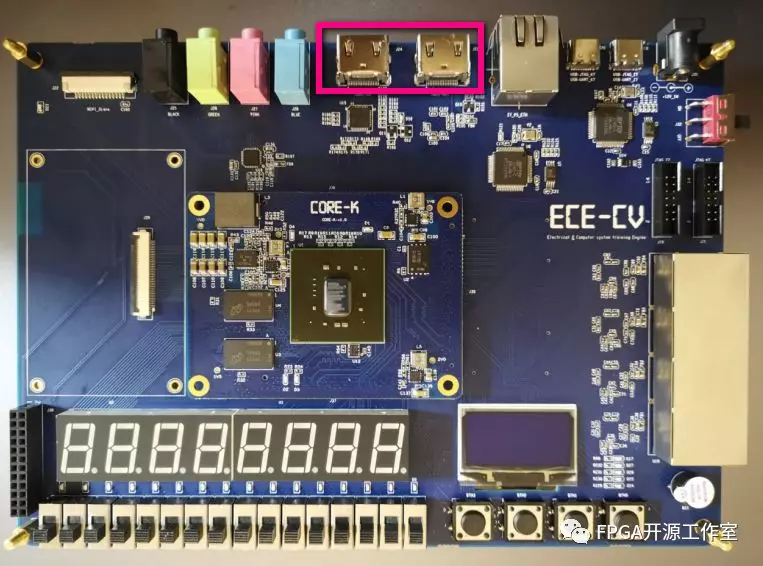

本实验基于ECE-CV K7-75T FPGA开发板实现。

软件使用Vivado 2018.1。

基于HDMI的视频流输入输出实验

1 HDMI概述

HDMI高清多媒体界面(英语:High Definition Multimedia Interface)是一种全数字化视频和声音发送接口,可以发送未压缩的音频及视频信号。HDMI可用于机顶盒、DVD播放机、个人计算机、电视游乐器、综合扩大机、数字音响与电视机等设备。HDMI可以同时发送音频和视频信号,由于音频和视频信号采用同一条线材,大大简化系统线路的安装难度。

图1 HDMI硬件实物

如图1,红框为ECE-CV板的HDMI输入输出接口,最高支持到1080P@60HZ的图像输入和输出功能。

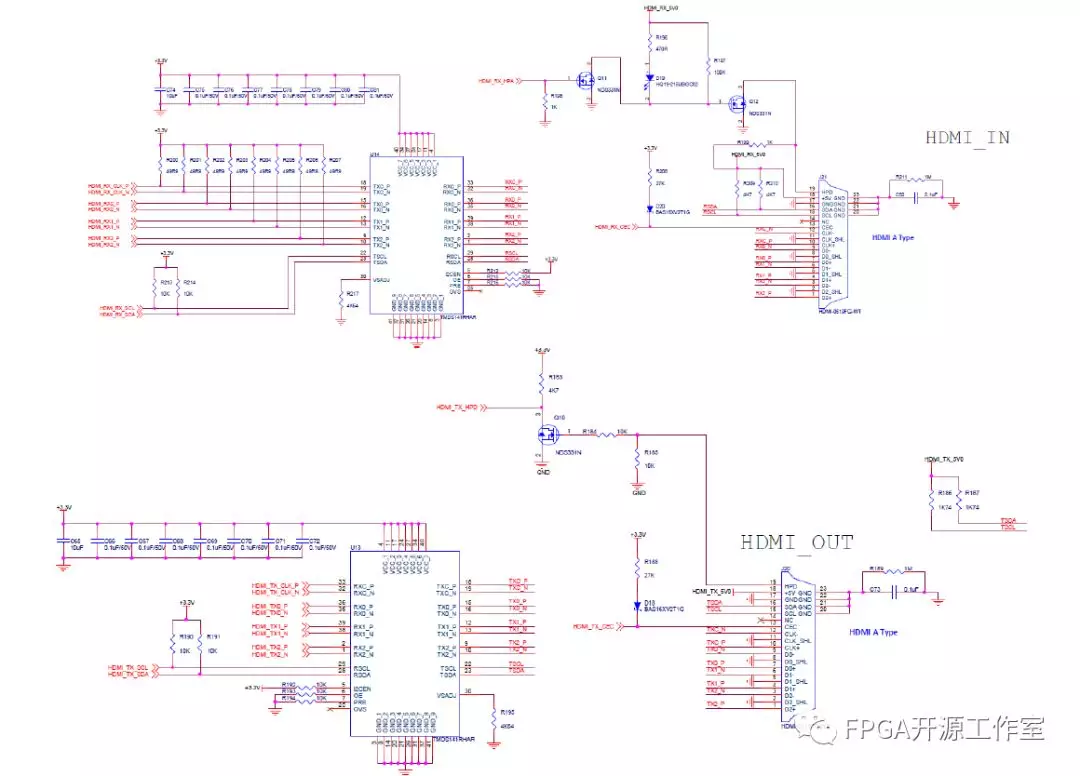

图2 HDMI_IN 和HDMI_OUT原理图

如图2所示为ECE底板的HDMI_IN和HDMI_OUT的原理图,下面对ECE-EDA和ECE-CV的HDMI接口的引脚介绍如表1所示:

表1 ECE-CV板HDMI接口引脚介绍

|

信号名称 |

Kintex7引脚标号 |

电平 |

备注 |

|

HDMI_RX0_P |

R25 |

TMDS_33 |

HDMI接收数据0正 |

|

HDMI_RX1_P |

T24 |

TMDS_33 |

HDMI接收数据1正 |

|

HDMI_RX2_P |

T22 |

TMDS_33 |

HDMI接收数据2正 |

|

HDMI_RX_CLK_P |

N21 |

TMDS_33 |

HDMI接收时钟正 |

|

HDMI_RX_CEC |

P24 |

LVCMOS33 |

HDMI遥控器信号 |

|

HDMI_RX_HPD |

N24 |

LVCMOS33 |

HDMI热插拔检测信号 |

|

HDMI_RX_SDA |

M25 |

LVCMOS33 |

HDMI IIC数据 |

|

HDMI_RX_SCL |

L25 |

LVCMOS33 |

HDMI IIC时钟 |

|

HDMI_TX0_P |

M21 |

TMDS_33 |

HDMI发送数据0正 |

|

HDMI_TX1_P |

N19 |

TMDS_33 |

HDMI发送数据1正 |

|

HDMI_TX2_P |

P16 |

TMDS_33 |

HDMI发送数据2正 |

|

HDMI_TX_CLK_P |

P23 |

TMDS_33 |

HDMI发送时钟正 |

|

HDMI_TX_CEC |

L24 |

LVCMOS33 |

HDMI遥控器信号 |

|

HDMI_TX_HPD |

M24 |

LVCMOS33 |

HDMI热插拔检测信号 |

|

HDMI_TX_SDA |

U16 |

LVCMOS33 |

HDMI IIC数据 |

|

HDMI_TX_SCL |

N16 |

LVCMOS33 |

HDMI IIC时钟 |

2 HDMI IP介绍

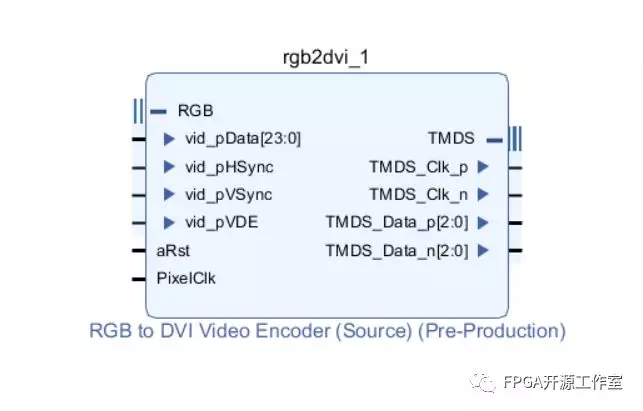

如图3所示,rgb2dvi IP 实现RGB并行图像数据信号转换成串行差分信号输出。1920*1080P@60HZ的像素时钟为148.5MHZ。

图3 rgb2dvi IP

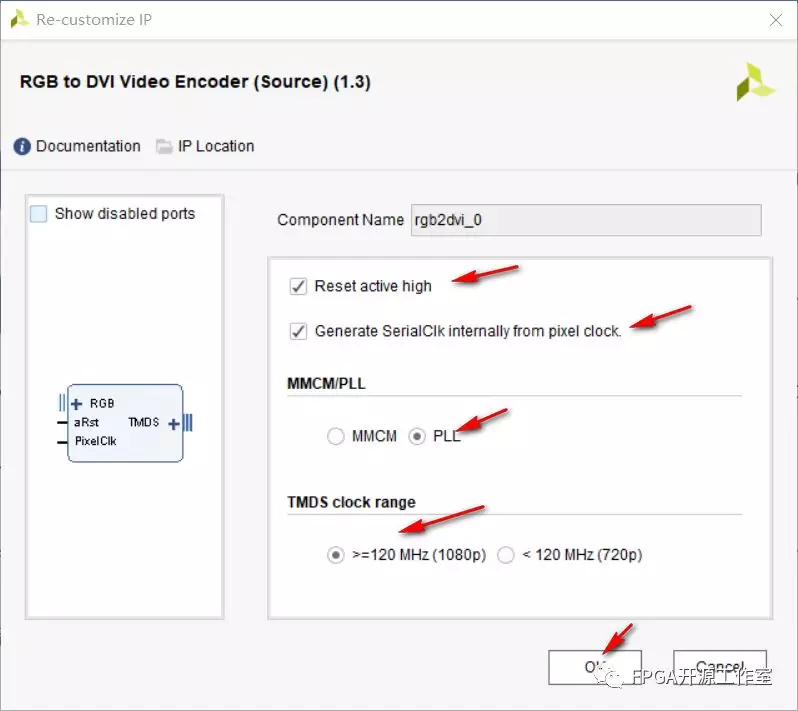

图4 rgb2dvi IP设置

如图4所示,其他项均默认,TMDS clock range 选择大于120MHZ。

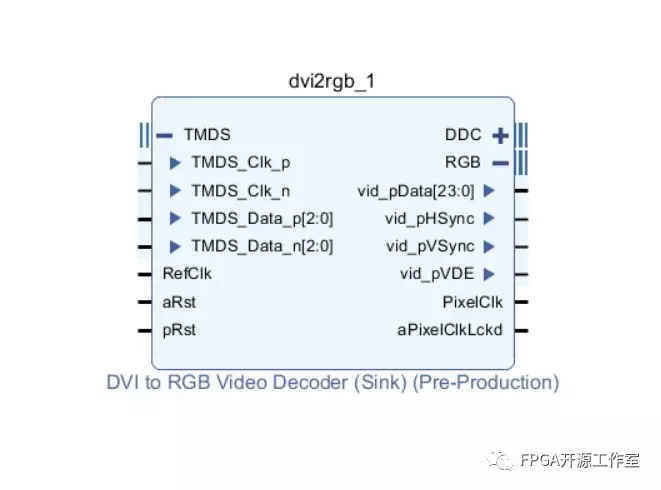

如图5 Dvi2rgb IP实现串行视频差分信号转RGB并行图像数据。参考时钟为200MHZ。

图5 dvi2rgb IP

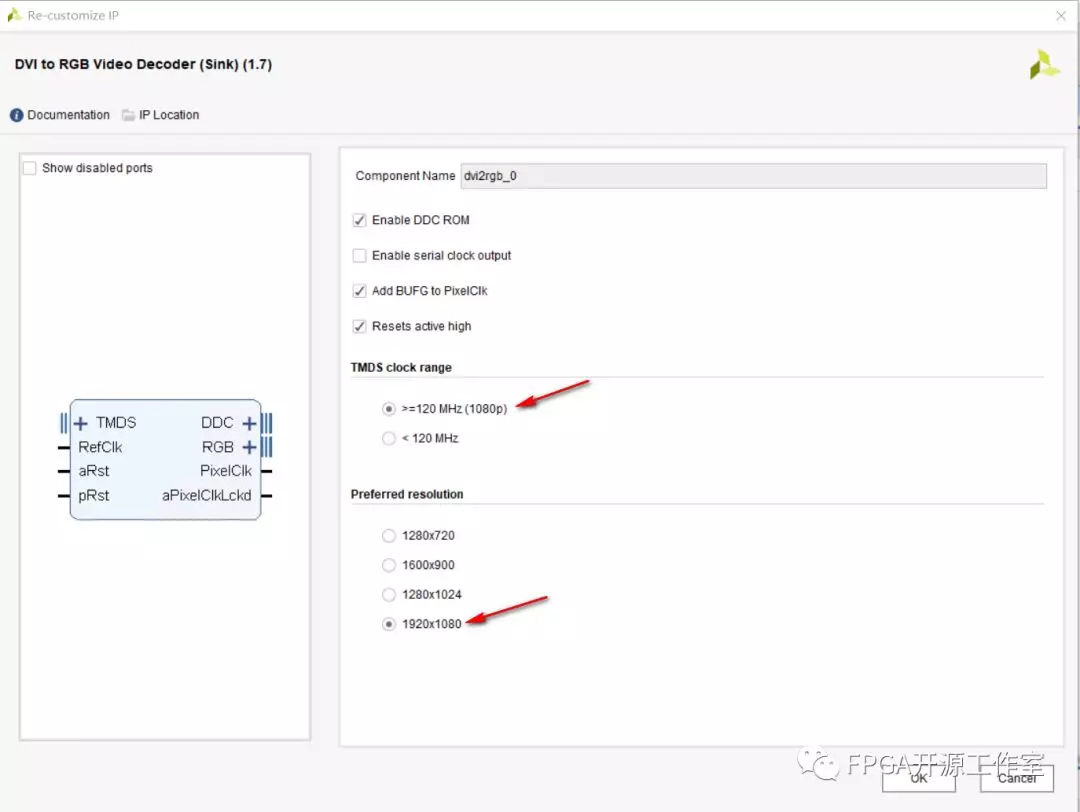

图6 dvi2rgb IP设置

如图6所示,TMDS clock range 选择大于120MHZ,Preferred resolution选择1920*1080。

3 HDMI输入输出实验系统搭建

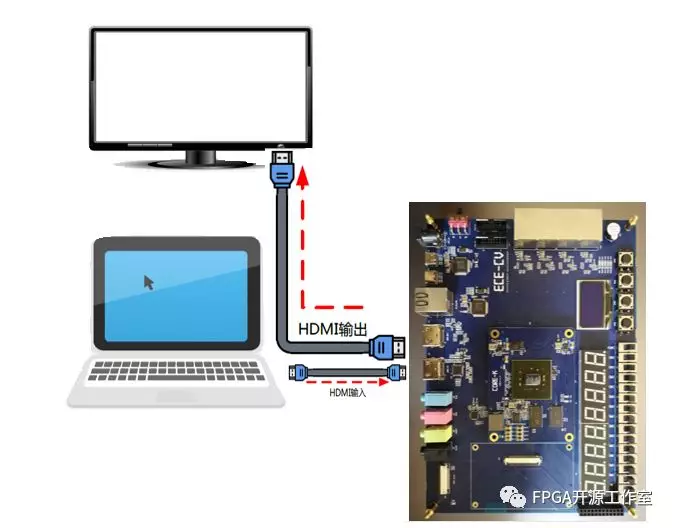

笔记本电脑的HDMI输出1080P@60HZ的视频ECE-CV平台,经过HDMI_IN到核心板再到HDMI_OUT再到显示屏,显示屏正常输出视频。整个硬件平台如图7所示。

图7 ECE-CV数字图像处理硬件平台

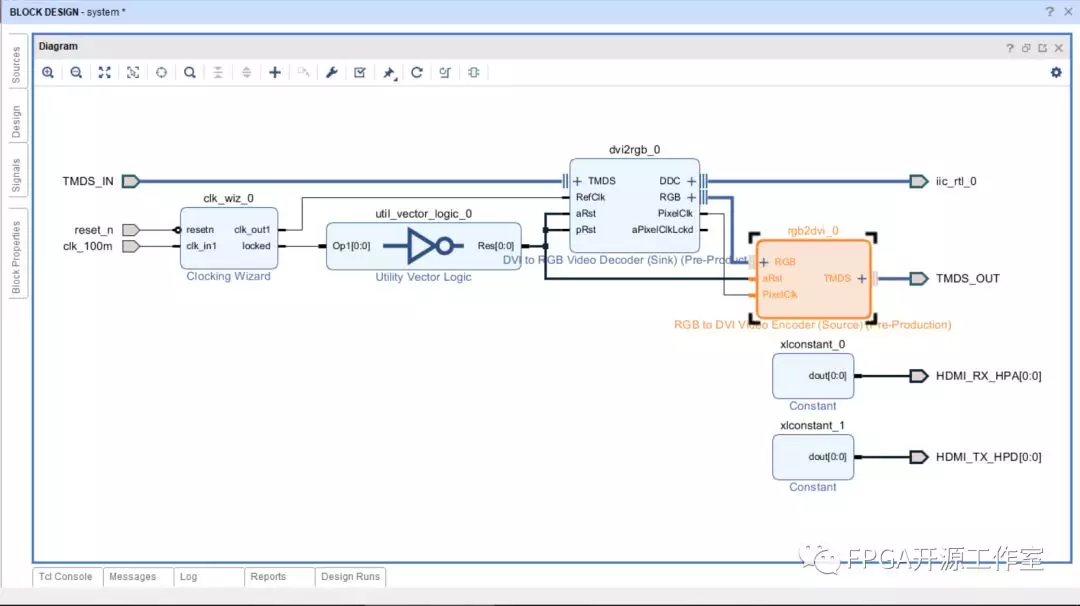

如图8,为HDMI_IN_OUT最终系统连接图。

HDMI_IN_OUT系统由外部OSC输入100MHZ时钟,经过Clock Wizard IP的倍频输出200MHZ时钟到Dvi2rgb IP作为参考时钟,同时输出reset_n(locked )信号为全局复位信号。复位信号(reset_n)经过Utility Vector Logic IP取反输出‘1’复位‘0’有效rst信号。Dvi2rgb IP的参考时钟(Refclk)为200MHZ,差分数据信号输入为TMDS_IN,经过Dvi2rgb IP转换为RBG888的VGA时序信号以及输出像素时钟(Pixelclk)。Rgb2dvi IP接收RBG888的VGA时序信号输出TMDS_OUT的差分数据信号。xlconstant IP为HDMI的输入和输出提供热插拔信号输出为‘1’。

图8 HDMI输入输出实验系统连接图

4 实验结果展示

文章转载自:FPGA开源工作室