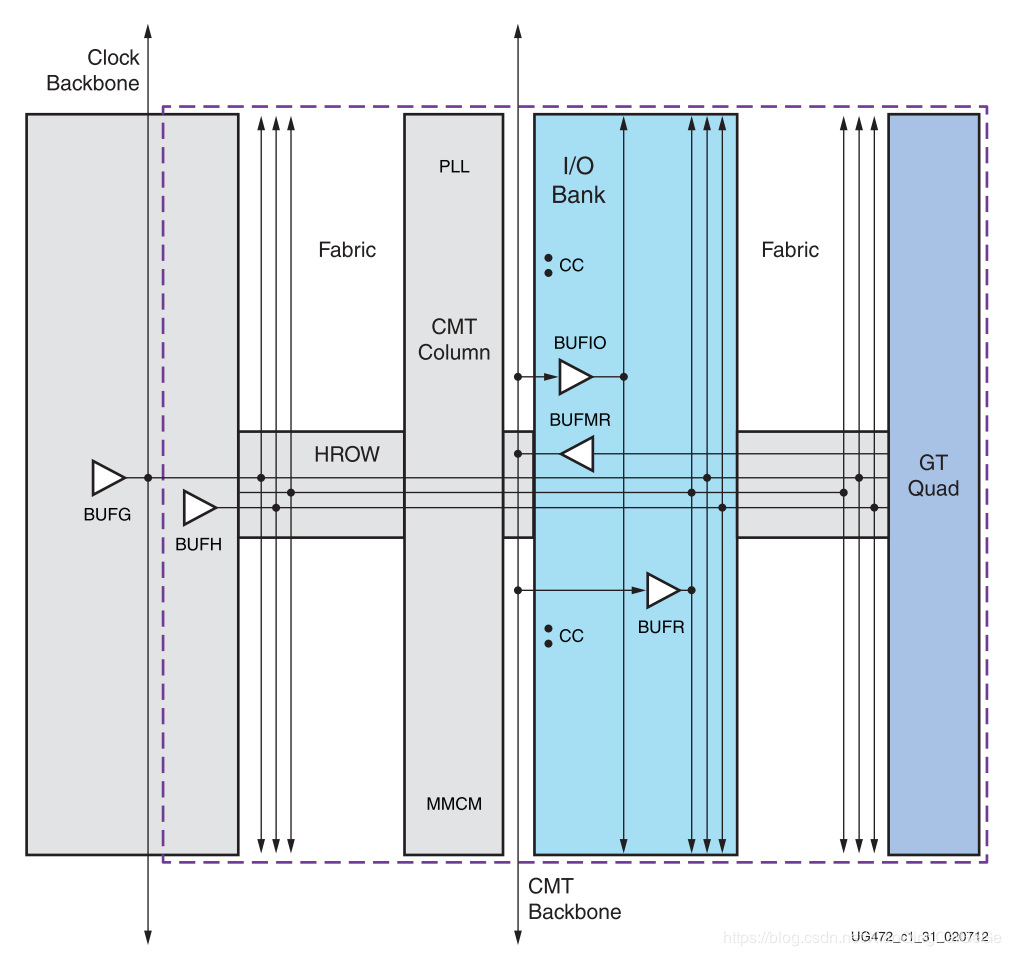

上一篇咱们介绍了7系列FPGA的整体时钟架构,知道了FPGA是由很多个时钟区域组成,时钟区域之间可以通过Clock Backbone 和CMT Backbone来统一工作。本篇咱们就说一下时钟区域的内部结构,如图1所示的虚线框内即为一个时钟区域:

1,BUFG即为全局时钟缓冲器,从图上看到,其输出时钟通过Clock

Backbone可以到达任意一个时钟区域,而且BUFG通过HROW到达时钟区域内部的每个逻辑单元。

2,BUFH即为水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。

3,BUFIO即为IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。

4,BUFR即为区域时钟缓冲器,其输出只能作用在一个时钟区域,相当于BUFH的阉割版。

5,BUFMR即为多区域时钟缓冲器,其输出作用在本时钟区域,还可以通过CMT Backbone作用在上下相邻两个时钟区域。

6,MMCM、PLL即时钟管理模块,用来消除时钟的延迟、抖动以及产生各种不同频率的时钟。

7,CC即为外部时钟输入管脚,其管脚在内部可以连接到BUFG、BUFR、BUFIO、BUFH、MMCM、PLL等,看具体的应用具体连接。下图所示为更为细致的CC管脚连接图。一个时钟区域有4对CC管脚,其中2对SRCC,2对MRCC。SRCC作为区域时钟使用时,只能连接本时钟区域的BUFR和BUFIO。而MRCC则还可以通过BUFMR作用在上下相邻的时钟区域。

咱们自己结合这几张图好好分析下,就会彻底明白一个时钟区域内的具体时钟构造了,祝大家好运!利用上述所讲,下篇咱们将介绍如何在不同应用中来操作时钟。

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主