AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

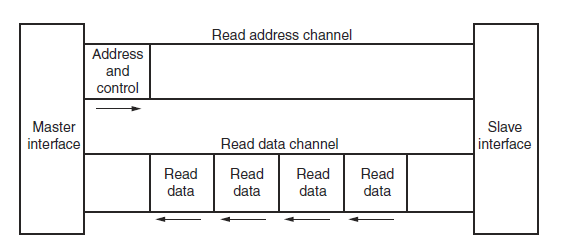

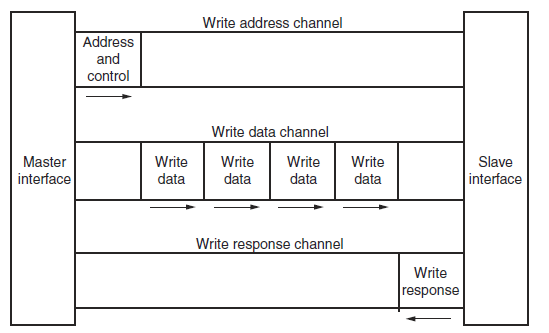

AXI协议是基于burst的传输,并且定义了5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接收信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

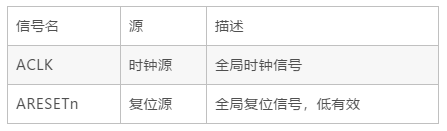

全局信号

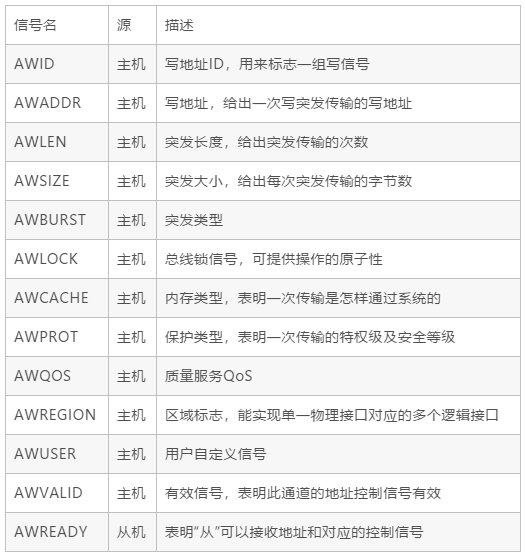

写地址通道信号

写数据通道信号

写响应通道信号

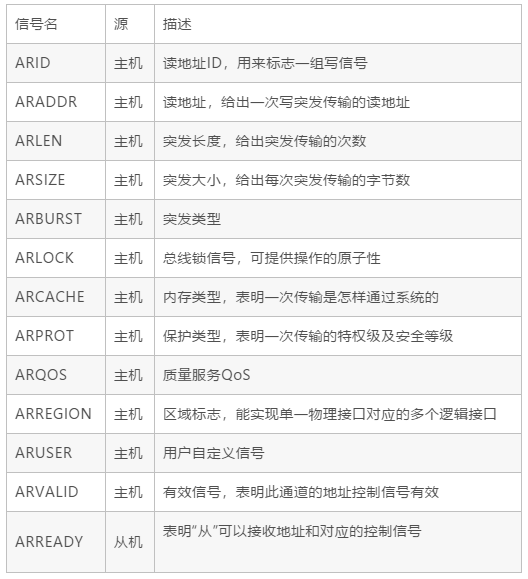

读地址通道信号

读数据通道信号

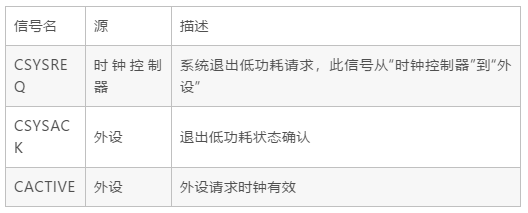

低功耗接口信号

未完待续......

本文转自: 瓜大三哥(微信号:xiguazai_tortoise),作者:米果不回来,转载此文目的在于传递更多信息,版权归原作者所有。