描述

Zynq UltraScale+ MPSoC TRM 包含一个详细介绍 PS 及 PL SYSMON 时钟的部分。

它说明 SYSMON 的数字参考时钟是 LPD_LSBUS_CLK:

“SYSMON 时钟由接口时钟驱动。接口时钟被划分为使用 CONFIG_REG2 [clock_divide] 位字段生成 ADC 时钟。

这是不正确的,将在 TRM 的未来版本中修复。

本答复记录详细描述了 PS 和 PL SYSMON 的时钟基础架构。

解决方案

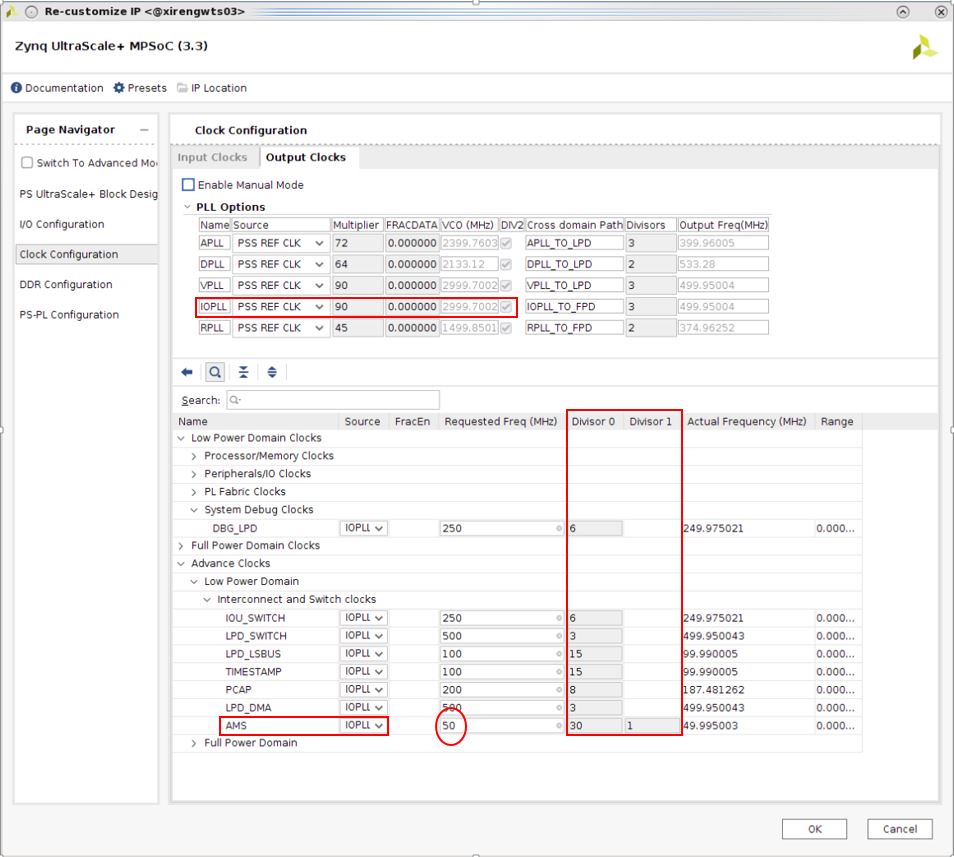

该图是 PS 和未实例化的 PL SYSMON 的时钟结构。

当未实例化数字时钟时,PSSYSMON_REF_CLK 会将其提供给 PSSYSMON 和 PL SYSMON。

该时钟是基于 PSSYSMON_REF_CTRL 寄存器中的设置生成的。

这个寄存器包含选择输入锁相环时钟的位。

输入时钟可以来自 RPLL 或 IOPLL(它们都配备了除以 2 的输出),也可以来自 DPLL_CLK_TO_LPD,后者是 DPLL 的一个分割版本。

这个除数可在 DPLL_TO_LPD_CTRL 寄存器中看到。

IOPLL 设置可在 IOPLL_CTRL 寄存器中看到。

RPLL 设置可在 IOPLL_CTRL 寄存器中看到。这些都是 CRL_APB 寄存器组的一部分。

PSSYSMON_REF_CTRL 还可设置两个分隔符 DIVISOR0 和 DIVISOR1,其可生成 PSSYSMON_REF_CLK。

然后可将 PSSYSMON_REF_CLK 传递给 SYSMON 单元,再在 SYSMON 配置寄存器中对其进行进一步划分,以生成 ADC 时钟。

还可以检查从 Vivado 中的处理器配置向导设置的时钟。

在这个示例中,可以看到 IOPLL 已被选中。

其 VCO 为 3000Mhz,而且启用了 DIV2 设置。这意味着将 1500Mhz 传递给 PSSYSMON_REF_CTRL 模块。

请求 PSSYSMON_REF_CLK 为 50MHz。

在本例中,DIVISOR0 设置为 30,而 DIVISOR1 设置为 1。