本文转载自: 傅里叶的猫 微信公众号

今天我们来研究一下D触发器都有哪几种类型?又对应什么样的代码?

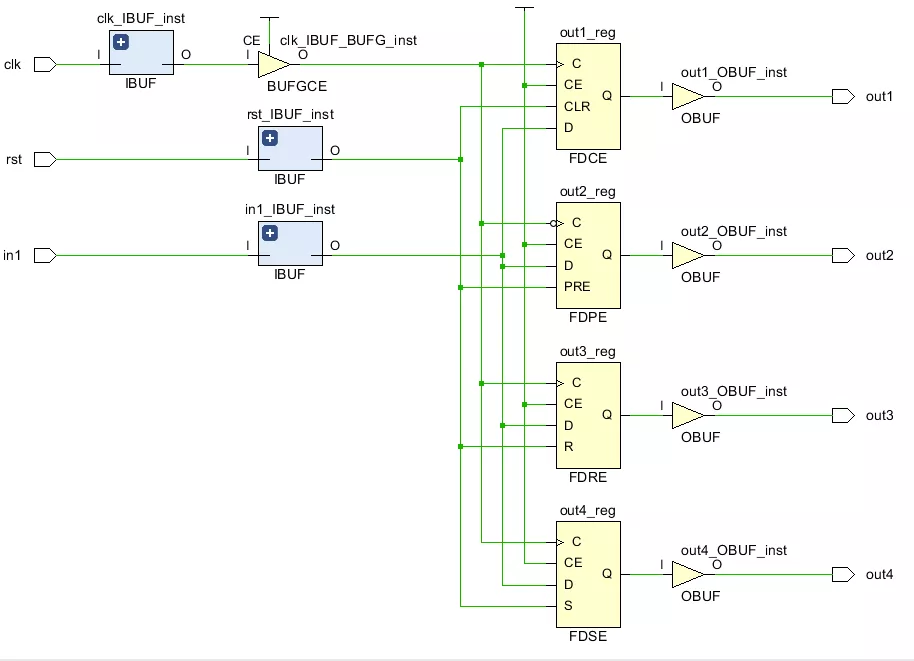

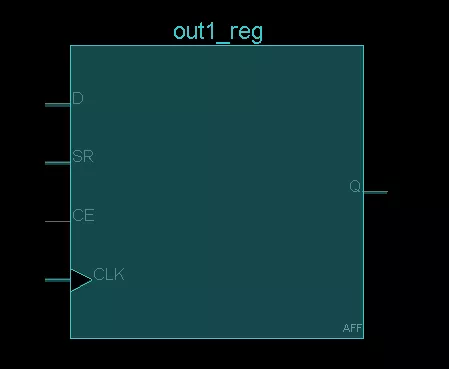

在Xilinx的FPGA中,D触发器是下面这个样子:

其中,D是数据输入端口,CE是使能端口,CLK是时钟输入,SR是Set/Reset的意思,可用作置位或者复位,置位和复位又分同步和异步,因此D触发器有如下四种应用类型:

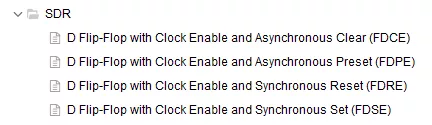

在Vivado的Language Templates中我们也可以看到,D触发器有下面四种类型:

那这四种触发器都对应什么样的代码?

module top(

input clk,

input rst,

input in1,

output reg out1,

output reg out2,

output reg out3,

output reg out4

);

// FDCE

always @ ( posedge clk or posedge rst)begin

if(rst)

out1 <= 1'b0;

else

out1 <= in1;

end

// FDPE

always @ ( negedge clk or posedge rst )begin

if(rst)

out2 <= 1'b1;

else

out2 <= in1;

end

// FDRE

always @ ( posedge clk )begin

if(rst)

out3 <= 1'b0;

else

out3 <= in1;

end

// FDSE

always @ ( posedge clk )begin

if(rst)

out4 <= 1'b1;

else

out4 <= in1;

end

endmodule

综合后: