软件版本:vitis2021.1(vivado2021.1)

操作系统:WIN10 64bit

硬件平台:适用AMD-XILINX A7/K7/Z7/ZU/KU系列FPGA

1 概述

在开发工程中,我们需要对一些信号进行debug调试,如果对于CPU的软件开发一般可以设置断点,但是对于FPGA来说,FPGA是无法设置断电的,但是FPGA可以通过内嵌的逻辑分析仪(ILA)IP以及虚拟(VIO)IO IP实现在线调试。

本教程内容是我们快速入口课程,目的是尽量通过一个demo教大家熟悉我们软件的一个基础的操作,所以我们本节课基于我们前面已经完成的demo内容,进一步扩展一些简单的功能,然后学习使用我们的ILA以及VIO来对我们的代码进行调试。

2通过ILA IP核观察信号

ILA(Integrated Logic Analyzer)集成逻辑分析器:即Vivado的在线逻辑分析仪,其借用了传统逻辑分析仪的理念以及大部分的功能,并利用FPGA 中的逻辑资源,将这些功能植入到FPGA 的设计当中。ILA是用IP核的形式实现的。

在线逻辑分析仪通过一个或多个探针(Probe)来采集希望观察的信号,然后通过片内的JTAG 硬核组件,来将捕获到的数据传送给下载器,进而上传到Vivado IDE 以供用户查看。Vivado IDE 也能够按照上述数据路径,反向地向FPGA 中的在线逻辑分析仪传送一些控制信号。

2.1添加ILA IP核

Step1:打开IP Catalog,也就是IP库

Step2:输入关键词ila,双击打开ILA IP核

Step3:这边我们简单的捕捉一下LED灯的变化,所以我们使用一个探针,采样深度选择2048,并不要使用Capture模式。Capture模式如果选择了,我们可以选择一个条件信号,仅条件信号满足设置要求时,才会进行采样或者触发操作,我们后续课程中会使用到这个模式,这边入门阶段不要求掌握。

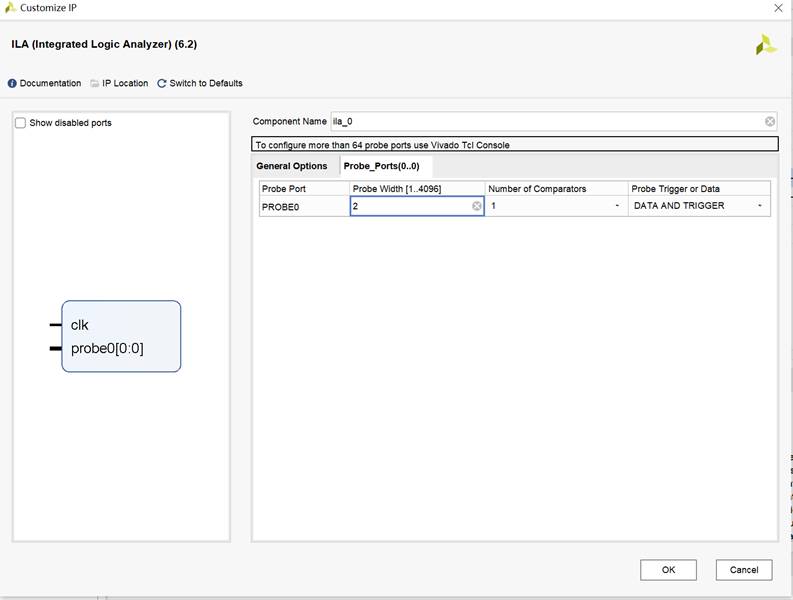

Step4:点击Probe_Ports,我们在这个页面下选择探针的位宽,我们本次打算捕捉2个LED灯信号,所以设置位宽为2。然后点击OK,IP核配置完成。

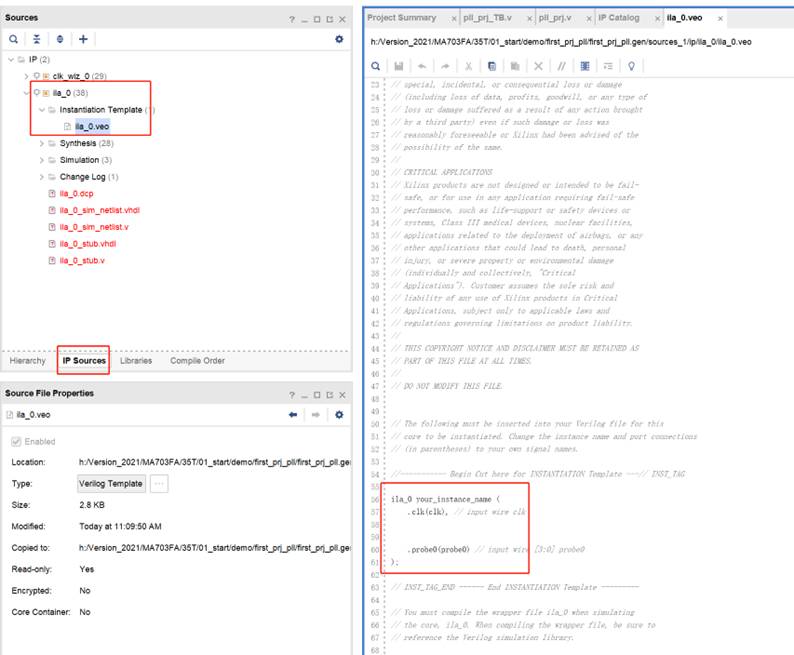

Step5:例化PLL IP核,将IP核添加进工程。

在工程中添加如下代码,点击保存。这边我们要注意,ILA IP核需要添加一个时钟,该时钟信号应该为观察信号的同步时钟。

ila_0 ila_led (

.clk(clk0), // input wire clk

.probe0(O_up_led) // input wire [1:0] probe0

);

到这里,我们的ILA IP核(在线逻辑分析仪)添加完成。

3学习使用VIO IP

Vivado中的VIO(Virtual Input/Output) IP核是一种用于调试和测试FPGA设计的IP核。它允许设计者通过使用JTAG接口读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核提供了一个简单易用的接口,使得用户可以轻松地与FPGA内部寄存器进行交互。通过使用VIO IP核,用户可以实时监视和修改设计中的信号,以便进行调试和验证。此外,VIO IP核还可以与其他IP核和设计组件配合使用,从而帮助设计者更好地理解和调试整个系统。

3.1添加VIO IP核

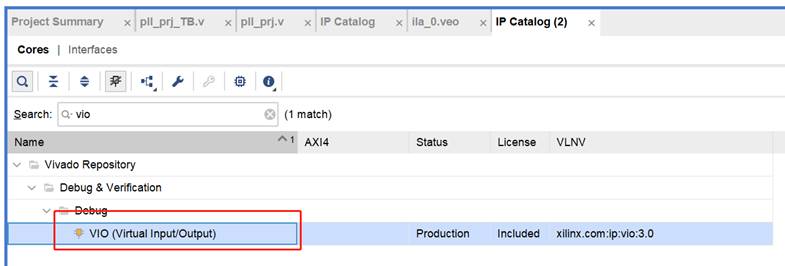

Step1:打开IP Catalog,也就是我们的IP库

Step2:输入关键词vio,即可找到我们需要使用的VIO IP核,双击对IP核进行配置。

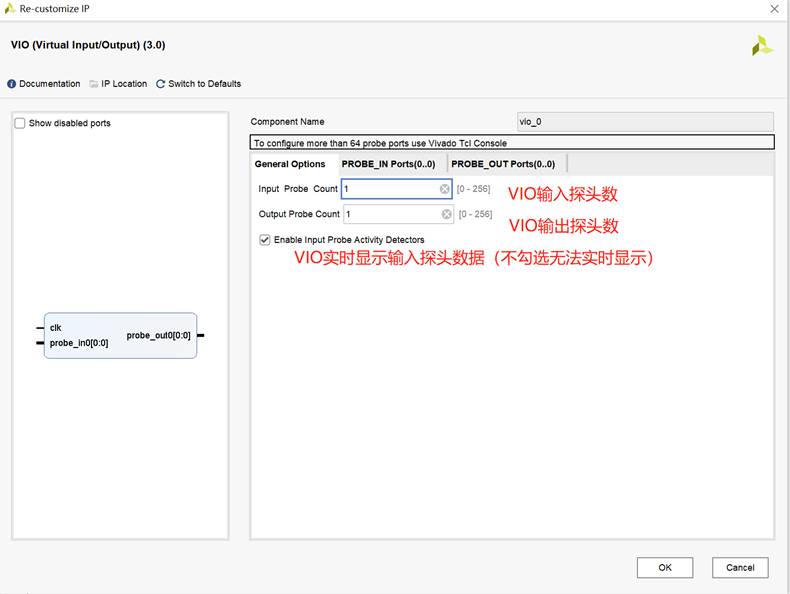

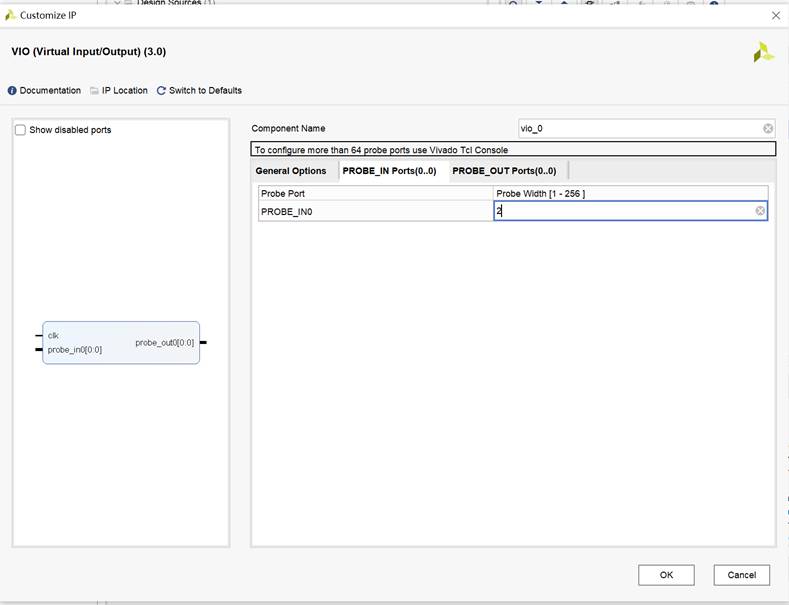

Step3:首先是对VIO的虚拟输入/输出引脚的个数的配置。

Input Probe Count:VIO输入探头个数,即输入到VIO,需要查看实时数据值的信号个数;

Output Probe Count:VIO输出探头个数,即输出给其他模块的信号个数;

Enable Input Probe Activity Detectors:输入探头变化检测。若勾选,则在后续调试过程中,某个输入信号发生变化时,则会出现数据变化的提示;若不勾选,则无输入数据变化提示(注意,这里输入数据是指输入到VIO模块中的数据);

另外,在这里有一点值得注意:输入/输出探头的最大个数为256,而在该界面下,最多可以生成64个输入/输出探头的VIO IP核,如果要生成大于64的VIO IP核,则需要通过Tcl脚本进行生成。

Step4:点击PROBE_IN_Ports,对输入探头的位宽进行设置,即我们需要观察的信号的位宽。我们需要观察的信号为2路LED灯的变化,所以位宽我们选择2。

Step5:点击PROBE_OUT_Ports,对输出探头的位宽进行设置,即输出到其他模块,用于计算或者控制的信号的位宽。我们这边打算输出的控制信号是控制LED转换的复位信号,所以需要将LED计数以及LED转换模块的复位信号修改成"restn",由于我们复位低电平有效,所以默认我们默认设置为0x1,我们可以通过手动修改这个值为0,来触发复位。

对VIO IP核配置完成后,点击OK,生成IP核。

Step6:例化PLL IP核,将IP核添加进工程。

添加后我们工程代码如下,点击保存,到这里,我们的VIO IP核添加完成。

使用"restn"可以操控VIO来进行复位操作,但是因为LED寄存器无法正常初始化,所以会影响仿真的正常状态,如果想正常使用仿真,还需要将"restn"改回"pll_lock"

`timescale 1ns / 1ps

module pll_test(

input I_sysclk_p,//系统时钟输入

output [1:0]O_up_led//LED输出

);

wire clk0;

wire pll_lock;

reg [25:0] cnt;

//例化PLL模块

mypll mypll_u(

.reset(1'b0), //PLL复位

.clk_out1(clk0), //PLL输出时钟

.locked(pll_lock), //PLL锁住

.clk_in1(I_sysclk_p) //PLL输入时钟

);

assign O_up_led = {cnt[25:24]};//输出计数器的高位用于驱动LED

//计数器

always @ (posedge clk0 or negedge restn)begin

if(restn==1'b0)

cnt <= 26'd0;

else

cnt <= cnt + 1'b1; //cnt power on initial value is all 1

end

ila_0 ila_led (

.clk(clk0), // input wire clk

.probe0(O_up_led) // input wire [3:0] probe0

);

//VIO IP例化

vio_0 vio_led (

.clk(clk0), // input wire clk

.probe_in0(O_up_led), // input wire [1 : 0] probe_in0

.probe_out0(restn) // output wire [0 : 0] probe_out0

);

endmodule

4直接添加信号法

我们除了添加ILA IP去观察信号,我们还可以直接添加观察信号。下面我们就介绍一下这种方式。

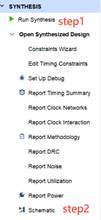

Step1:打开RTL原理图,如果你的Schematic选项是灰色的,说明你没有综合,你需要先综合,再打开RTL原理图。

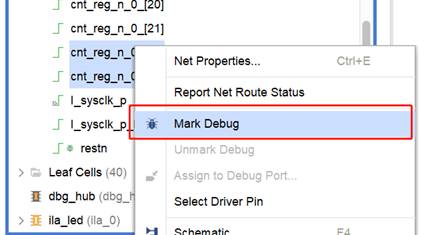

Step2:完成后,点击展开Nets,我们可以看到很多信号,有的信号上面有一个Debug的标志,是因为我们之前已经设置过ILA IP ,综合后认为该信号已经Debug,而且右键也无法重复设置Mark Debug

Step3:找到我们需要添加的信号寄存器信号,右键,Maek Debug。

Step4:设置完成后,寄存器信号前多了一个Debug标志,表示该信号设置成功,点击保存。

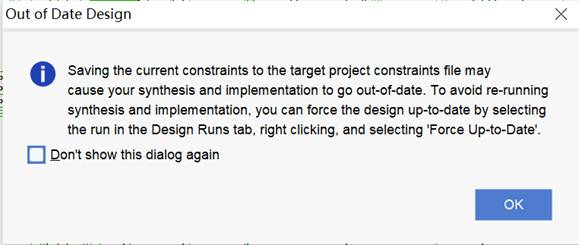

Step5:提示我们有更新,点击OK。

Step6:由于这种Debug方式是将Debug信息写入XDC文件的方式,所以提示我们需要更新XDC文件,我们可以选择覆盖现有的XDC文件,该选项并不会删除我们现有的XDC文件约束,而是将Debug信息添加在XDC约束后面,所以我们选择Overwrite。(如果没有该选项,说明你之前已经设置了默认添加的xdc文件)

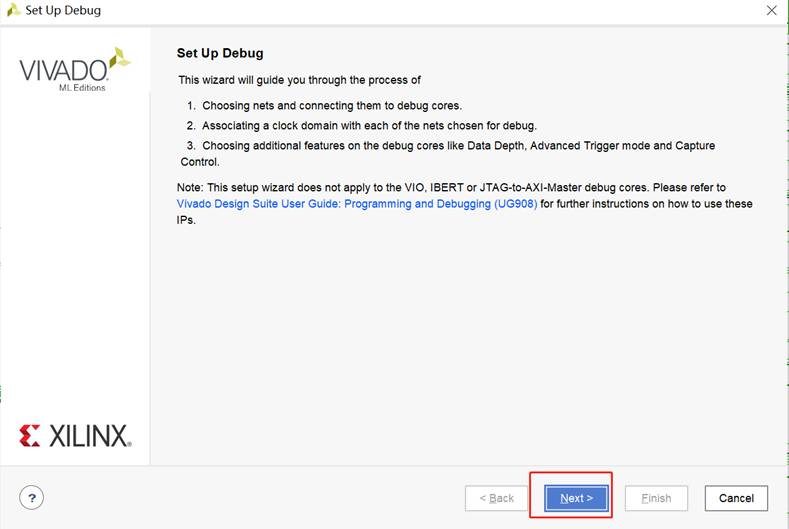

Step7:点击Set Up Debug,对我们刚才添加的BUG信号进行采样配置。

Step8:点击Next。

Step9:出现我们添加的信号,我们保持默认,点击Next。

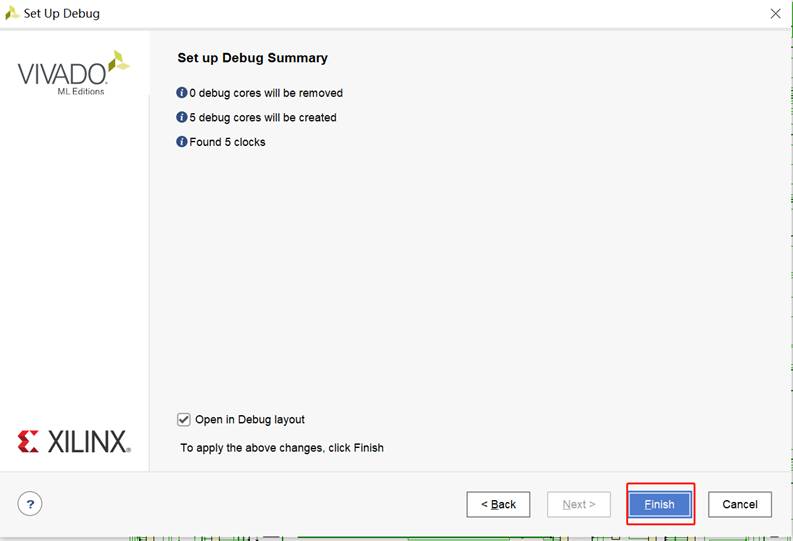

Step10:将采样深度设置为2048,其他保持默认,点击Next。

Step11:点击Finish,配置结束。

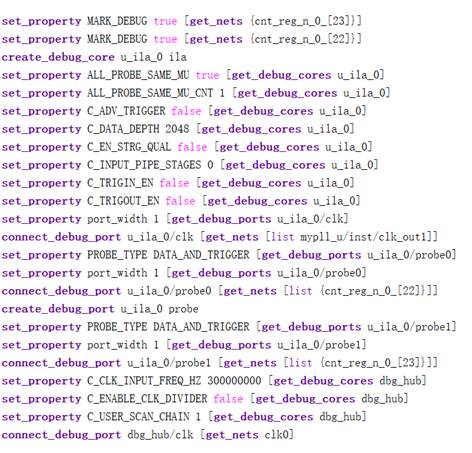

Step12:等待配置完成后,点击xdc文件可以看到我们信号的配置信息。

到此我们直接添加信号法完成。

5编译测试

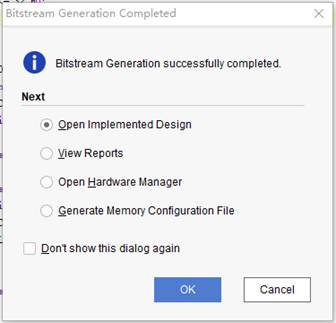

保存,点击开始编译,点击OK,开始编译,等待编译完成。

6下载程序

Step1:给开发板通电,并且连接下载器

Step2:单击OpenTarget 然后单击Auto Connect

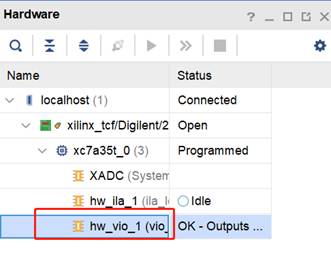

Step3:连接成功后如下图所示:

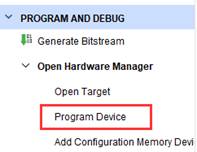

Step4:单击Program Device

Step5:单击选择上图的 FPGA,再单击Program Device,并且选择bit文件

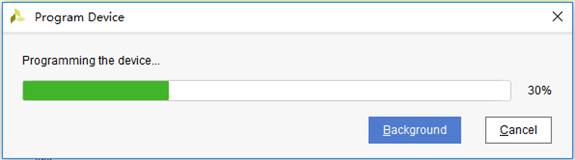

Step6:下载过程

6.1 ILA 使用

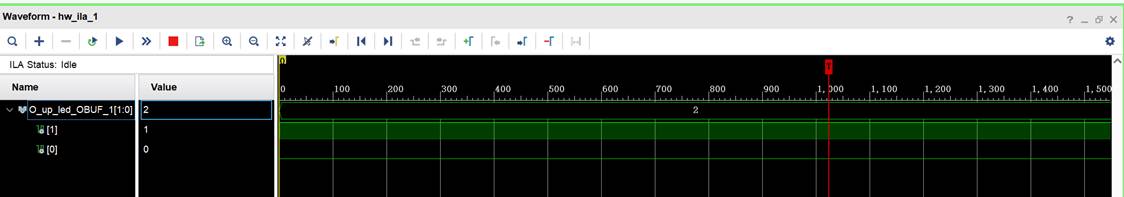

点击RUN就能观察到信号,但是我们的LED变换非常慢,加上我们设置的ILA深度比较小,所以我们仅仅只能观察到LED的某个时间的状态。

但是本教程主要是教会大家如何使用ILA,所以大家学会如何操作即可。

6.2 VIO 使用

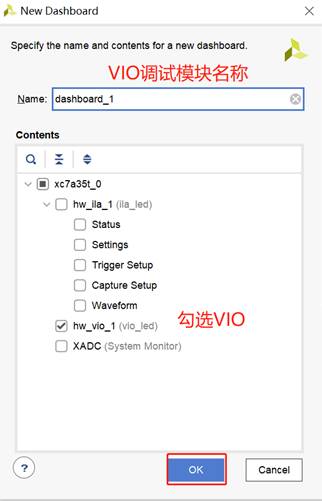

Step1:双击VIO模块,添加进入VIO调试

Step2:选择VIO模块窗口的名称,然后点击OK即可,这边我们保持默认

Step3:添加信号进入观察窗口

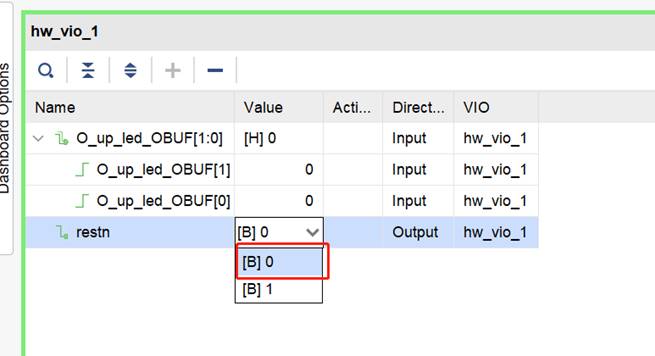

Step4:我们可以看到,LED信号随着时间不断的变化,同时我们的复位信号可以手动调节

Step5:手动调节restn信号为0,进行复位,观察到开发板所有的LED全部熄灭,LED信号全部为0。

Step5:手动调节restn信号为1,完成复位,开发板上LED灯闪烁恢复正常。

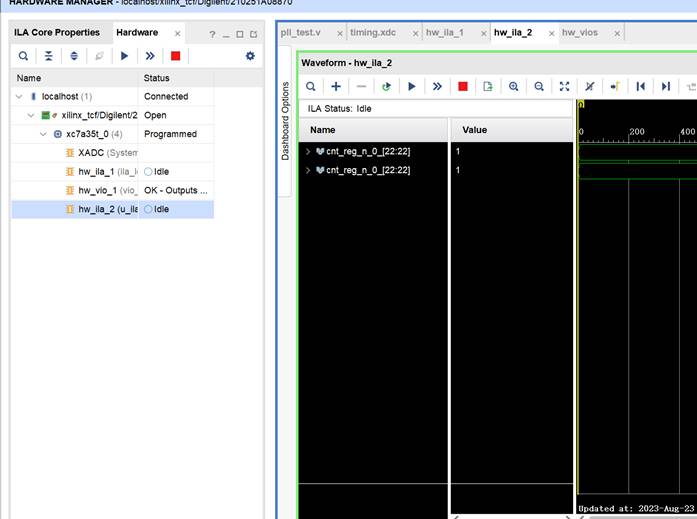

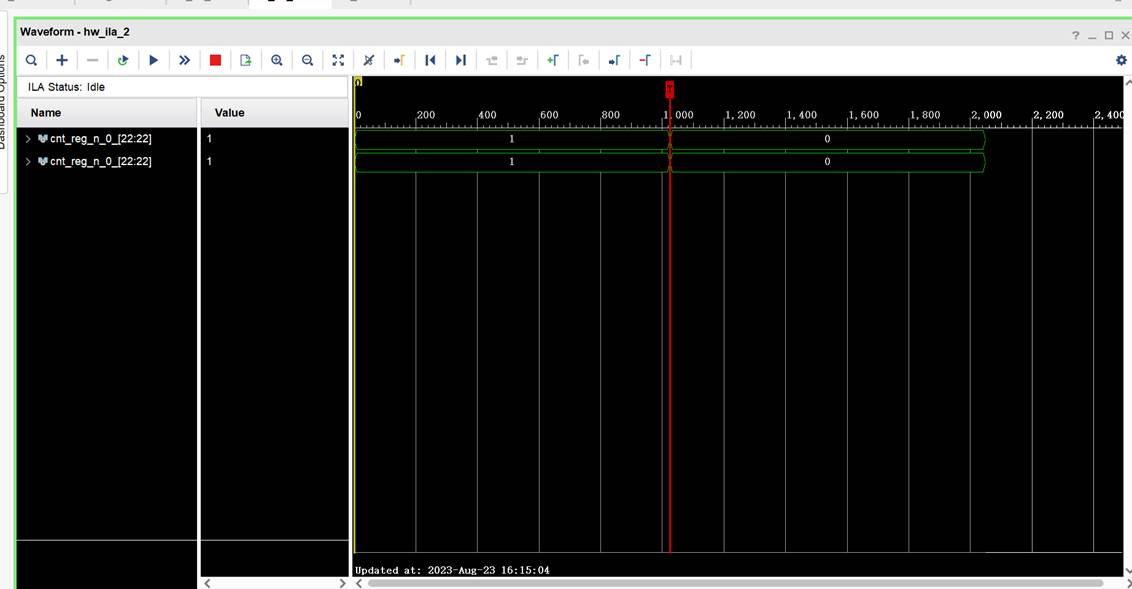

6.3 手动添加信号法使用

我们观察到我们手动添加的ila也正常产生。

Step1:设置触发条件为0时触发。

Step2:点击RUN信号触发。

7本章小结

本章节主要学习了两种方法添加ILA以及ILA IP、VIO IP等调试工具的使用方法。

本文转载自:uisrc.com