作者:Duoqiang Liu 来源:FPGA算法工程师

本文系摘录自《RFSoC SDR Book》第四章——DSP Fundamentals,略有改动。

下面将介绍采样(Sampling)的基本概念。

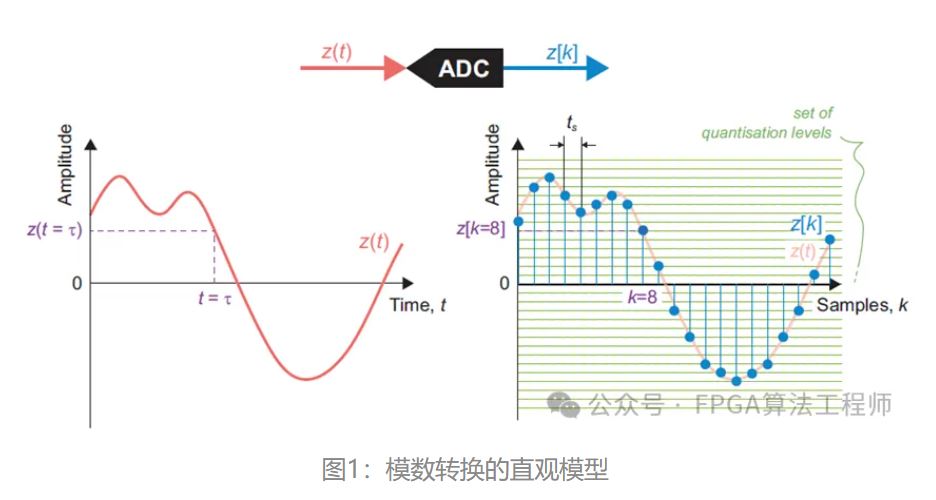

采样是将模拟信号转换为数字等效信号时发生的两个过程之一(另一个是量化,将在后续文章中介绍)。我们可以认为采样是将信号的时间轴转换为一组离散的时间瞬间,而量化将其幅度转换为一组离散的可表示的幅度值。这个简单的模数转换模型如图1所示,其中模拟信号![]() 通过ADC产生数字等效信号

通过ADC产生数字等效信号![]() 。

。

如图1左侧所示,模拟信号被认为是连续时间的,这意味着它的幅度是在所有时间内定义的,可以在任意时间点测量或表示。

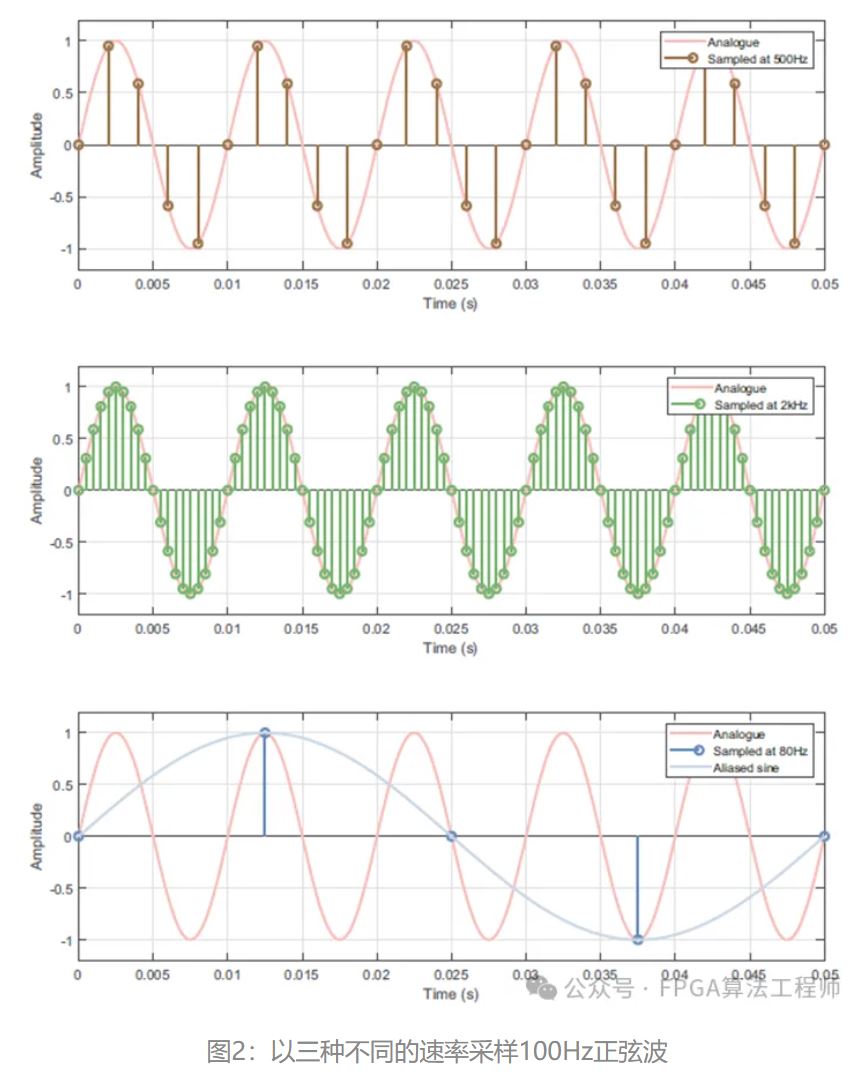

当转换到数字域时,如图1右侧所示,信号在时间上被表示为离散的时刻,这些时刻被采样周期 隔开。这个转换过程称为采样。采样周期

隔开。这个转换过程称为采样。采样周期 与采样频呈反比关系,如下式所示。请注意,术语采样率也很常见,并且可以与采样频率互换使用。

与采样频呈反比关系,如下式所示。请注意,术语采样率也很常见,并且可以与采样频率互换使用。

量化是ADC中一个独立但并发的过程,它将每个样本的幅度转换为最接近的可表示电平(图1中可用的量化电平集用绿色表示)。

1.1采样率选择

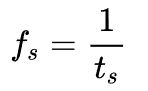

适当采样频率的选择主要受待处理信号的频率含量的影响。采样太慢,信号信息不能被正确捕获;采样太快,处理信号所需的操作不必要地膨胀。举一个简单直观的例子,考虑如图2所示的100HZ正弦波,它以三种不同的速率采样。

如果我们以2KHZ采样这个正弦波(如图2所示),信号肯定会被忠实地捕获(我们可以清楚地看到样本与原始正弦波的形状密切对应),然而,也许这是一个比需要的更高的速率?每个正弦波周期20个样本实际上远远超过了所需的最小值,并且意味着应用于信号的任何后续处理操作的计算开销。这可能通常需要进行数字滤波之类的操作。

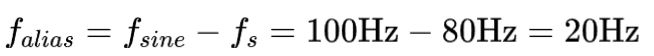

在另一个极端,80HZ的采样率(如图3所示)似乎是不够的。这将提供少于一个正弦波周期的样本,事实上,正弦波不能准确地从这个速率的样本重建。如果以80HZ的频率采样,那么实际上会感知到较低频率的正弦波。这种效果通常被称为混叠。在我们当前的示例中,混叠信号的频率为20HZ,其与正弦波频率和采样率的关系为

虽然混叠通常被认为是一种不受欢迎的效果,但在某些情况下,它可以被故意利用,这将在后面讨论。

最后,500HZ的采样率(第一张图)可能看起来“大致正确”。在这种情况下,每个正弦波周期有五个样本,这样可以很好地平衡准确捕获正弦波,并保持合理的低计算率。

1.2 信号频率范围术语

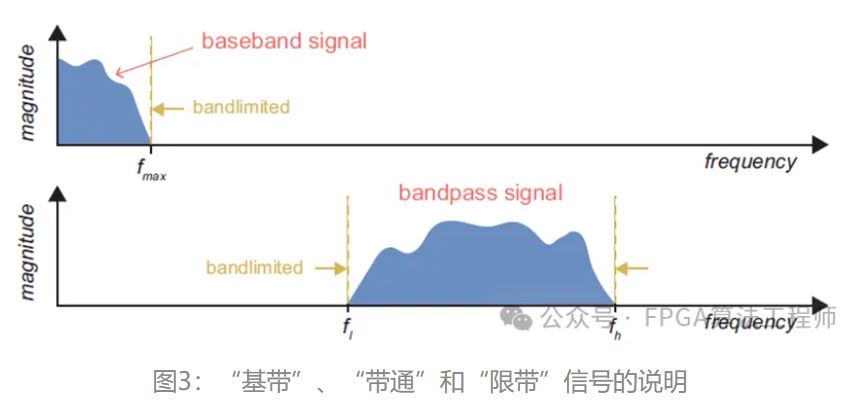

在这种采样率的背景下,定义一些描述信号中存在的频率范围的关键术语是有用的。图3为频谱示意图中两个信号的频域内容。

首先,当提到最低频率成分为或接近0HZ的信号时,称该信号为“在基带”,或“基带信号”。基带信号的示例包括传感器数据,例如来自电力系统的测量电压和电流、音频信号和未调制通信信号。

通常在通信中,我们分别考虑正在被发射机或接收机调制或解调的信号,并且它们没有任何接近0HZ的分量。可以应用于这些信号的一个术语是带通,反映信号占据一个频率范围,不接近0HZ(类似于被带通滤波器滤波的信号)。基带和带通信号也可以被称为带限信号,这意味着信号能量被包含在特定的频率范围内。

1.3 奈奎斯特采样理论

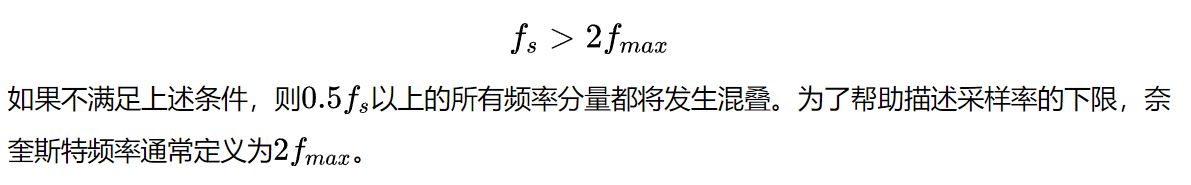

为了避免混叠,奈奎斯特采样定理给出了最小可能采样频率的一个更正式的定义。奈奎斯特采样定理指出,为了准确地保留所有的信号频率内容,基带带宽有限的信号必须以大于信号中存在的最大频率分量的两倍进行采样,即:

回到我们100HZ正弦波的例子,在这种情况下,根据奈奎斯特采样定理,需要的最小采样频率超过200HZ有趣的是,如果我们观察以250HZ采样率采集的样本(作为示例),那么与正弦波的对应关系可能不清楚;从人类检查的角度来看,这些样本在时域波形中不“看起来像”正弦波。然而,重要的是,原始的正弦波被这些样本在数学上完全捕获,并且信号的模拟版本可以被完美地重建。

回到我们100HZ正弦波的例子,在这种情况下,根据奈奎斯特采样定理,需要的最小采样频率超过200HZ有趣的是,如果我们观察以250HZ采样率采集的样本(作为示例),那么与正弦波的对应关系可能不清楚;从人类检查的角度来看,这些样本在时域波形中不“看起来像”正弦波。然而,重要的是,原始的正弦波被这些样本在数学上完全捕获,并且信号的模拟版本可以被完美地重建。

奈奎斯特采样理论也可以应用于带通、带限信号。信号的带宽定义为存在的最高和最低频率分量之间的差,分别用fh和fl表示。假设采样发生在带宽的两倍以上,即:

参照图3,则可以保留信号中的所有信息。这是通过欠采样技术实现的,隐含地依赖于混叠效应,并在适用的奈奎斯特区域内对信号进行校准。

1.4 奈奎斯特区域和混叠

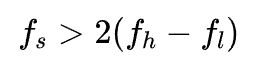

混叠以基于奈奎斯特区域(Nyquist Zones)的规则模式发生,这是频域中带宽为0.5fs的分区。根据奈奎斯特采样定理,可以定义任意数量的奈奎斯特区域,但只能直接表示第一个奈奎斯特带中的采样信号。由于混叠,出现在较高奈奎斯特区域中的任何信号分量都被“折叠”到第一奈奎斯特区域中。

为了考虑一些简单数字的例子,让我们假设采样率为200HZ。Nyquist Zone的宽度为100HZ,其中第一个Nyquist Zone的范围从0到100HZ,第二个Nyquist Zone的范围从100HZ到200HZ,以此类推,如图4所示。

理想的ADC采样频率为200HZ,因此,任何频率小于100HZ的输入信号都将被完美捕获,驻留在第1奈奎斯特区域。如果将100HZ和200HZ之间的信号频率应用于ADC,则这些组件将经历混叠,从而产生0到100HZ范围内的项(换句话说,第二个奈奎斯特区域的组件将折叠到第一个奈奎斯特区域)。由于在0.5fs 或100HZ处有一个对称点,混叠项的频率是可预测的,如图5所示,这说明了混叠的影响。

欠采样技术可用于利用混叠,并故意将带通信号折叠到奈奎斯特1区。在通信环境中,这种技术可以在接收机中用作将中频或射频调制信号转换为基带的一种手段(通常这被称为直接下变频)。图6的上轴显示了这种技术的一个示例,用紫色表示。

下变频信号的一个主要优点是,后续处理阶段所需的采样率可能会大大降低,这可以减少功耗和计算负荷。该技术依赖于原始信号完全包含在单个奈奎斯特区域中,否则产生的频谱会被混叠分量的叠加所破坏,如图6的下轴所示。注意,当接收到的信号跨越两个奈奎斯特区域时,信号的两个独立部分都混叠到第一个奈奎斯特区域的上部,并且彼此叠加。

这些例子没有考虑频谱中存在的任何其他频率分量。然而,在使用这种方法进行下变频之前,对信号进行带通滤波也是明智的,这将消除任何存在于任何其他奈奎斯特区域的噪声或杂散频率成分,否则所有这些都会混叠到第一个奈奎斯特区域并降低所需信号的质量。

1.5 采样抖动

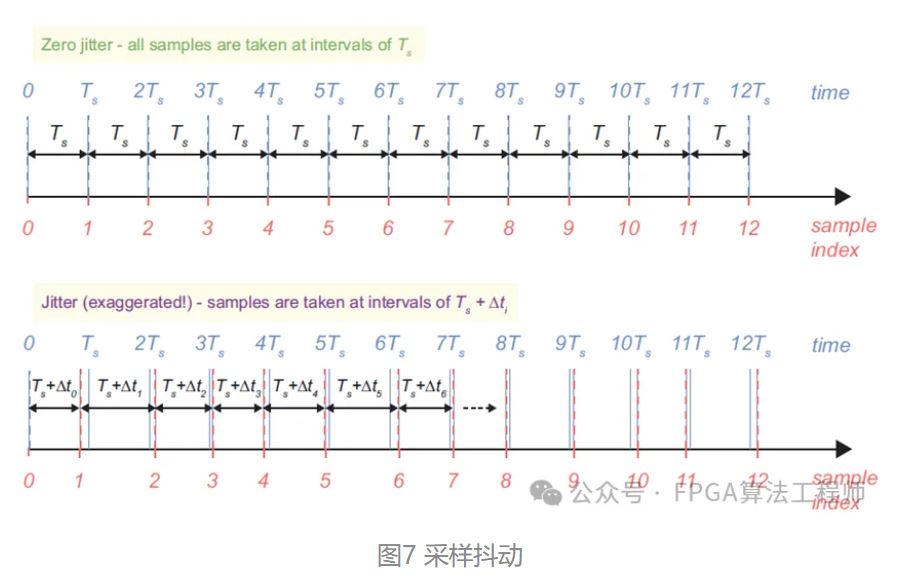

到目前为止,我们所有的采样都假设样本是完全定时的,在时间上有一致的分离。在实践中,ADC并不以这种完美的方式工作,并且在样本之间的周期应该有一些变化,如图7所示(注意,为了可视化的目的,采样周期的变化程度被夸大了)。

可变采样周期的这种影响被称为抖动,这是不希望的,因为输入信号的采样不是在理想的时间瞬间进行的。抖动也是DAC的一个特征,其中期望的输出样本在采样周期内会出现误差,因此不会在正确的时间瞬间产生。与理想采样时刻相比,由于采样时间错位,振幅值会产生相应的误差。因此,抖动可以被建模为噪声源。

高保真DAC和ADC在很大程度上最小化抖动,并且通常其他影响,如量化噪声占主导地位,即它们对所经历的总体噪声水平的贡献更大。然而,在非常高的采样频率下,抖动可能是一个值得注意的问题(采样时间的小偏差与采样周期成比例)。在本书的其余部分中,我们不会广泛考虑抖动,但是值得注意的是这种现象及其影响,特别是Zynq RFSoC可以在极高(GHz)采样率下工作,这自然更有可能经历抖动。

参考文献

1.Software Defined Radio with Zynq UltraScale+ RFSoC.