作者:蒋修国,来源:信号完整性

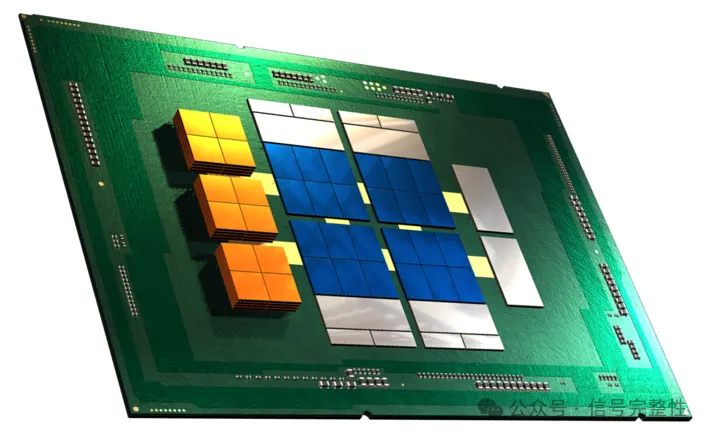

随着半导体行业接近摩尔定律的物理极限,传统单一芯片集成方式面临功耗、性能和成本的瓶颈。为解决这些挑战,Chiplet(芯粒)技术应运而生,成为异构集成的重要方向。Chiplet通过将功能模块化的芯片设计分拆为多个小芯片,利用先进封装技术实现高性能互连,从而提升系统灵活性和资源利用率。

Chiplet技术不仅能降低高性能芯片的研发成本,还能通过复用标准化模块缩短设计周期,适应不同应用场景的需求。此外,Chiplet在提升高带宽、低延迟性能的同时,显著降低了功耗,是推动数据中心、人工智能、5G等高性能计算领域发展的关键。

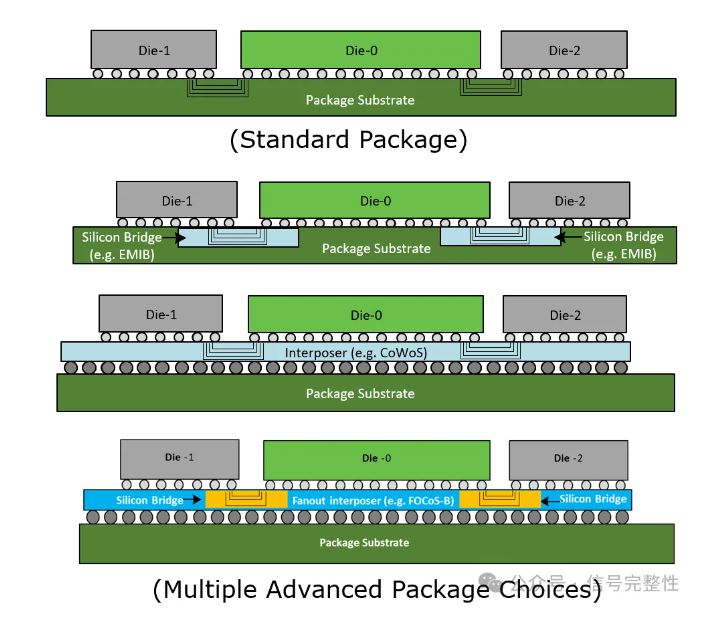

当前,包括UCIe、AIB和BoW在内的多种互连协议,为Chiplet互连和生态提供了可靠支持。随着先进封装技术如3D集成和2.5D封装的成熟,Chiplet正引领半导体行业从单片集成向模块化、多功能异构集成转型。

既然是不同模块或者是异构的集成,那么Chiplet技术的核心在于实现不同模块之间的高效互连。当前主流的Chiplet互连总线可以分为几大类别,如UCIe、BoW、AIB、CXL等,还有一些专有的互连总线。每种总线协议根据具体应用和性能需求有所侧重。

本文就给大家简要介绍下。

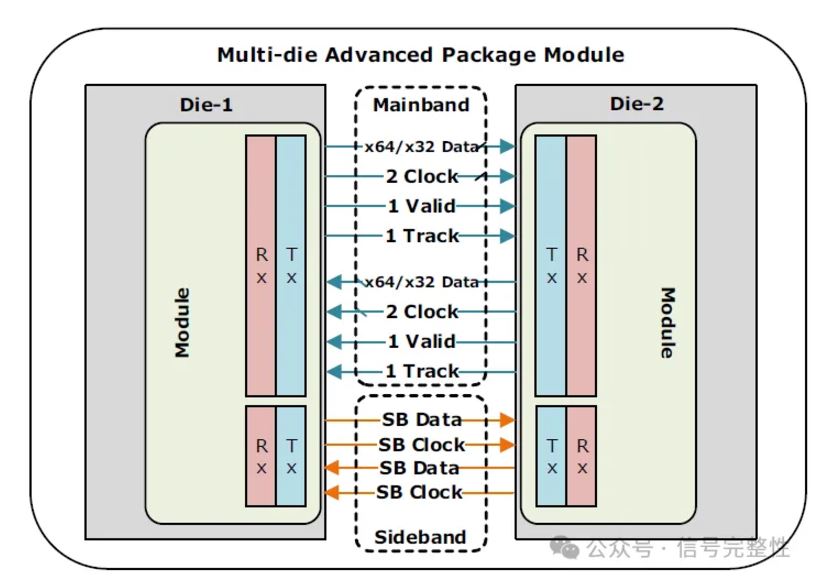

1. UCIe (Universal Chiplet Interconnect Express)

背景:由Intel、AMD、TSMC等行业领导者提出,是Chiplet互连的开放标准。

特点:

o面向通用用途,适用于高性能计算(HPC)、AI加速器等广泛应用。

o支持PCIe、CXL等协议的扩展。

o提供封装级低延迟互连,通过 Die-to-Die (D2D) 链接实现更高带宽和低功耗。

优势:高兼容性、标准化、支持多个封装工艺。

典型应用:CPU-GPU互连、内存与计算芯片的接口。

2. BoW (Bunch of Wires)

背景:由OCP(Open Compute Project)提出,专注于高效低成本的Chiplet互连。

特点:

o面向宽带宽、低延迟的互连需求。

o占用更少的功耗预算,适合需要极高性价比的芯片集成。

o提供物理层实现的灵活性(支持更广泛的封装技术)。

优势:简单、高效,适合经济型应用。

典型应用:数据中心中的加速器芯片、嵌入式系统。

3. AIB的背景与定义

背景:AIB (Advanced Interface Bus) 是由英特尔推出的一种用于芯片模块(Chiplet)间互连的开放式接口协议,是一种短距离、宽接口的互连协议,用于芯片之间的数据传输,优化了带宽和功耗的平衡,特别设计用于高速且低延迟的 Die-to-Die (D2D) 互连。

特点:

o高带宽:支持大规模的并行数据传输。单通道数据速率较低,但通过宽总线设计实现了高总带宽。

o低延迟:通过将互连距离控制在封装范围内(如 2.5D Interposer 或 EMIB 封装),大幅减少信号传播延迟。

o开放性:AIB协议是开放式的,支持不同供应商的模块间协作,提高生态系统的兼容性。

o低功耗:通过近距离互连设计降低了信号驱动功耗。

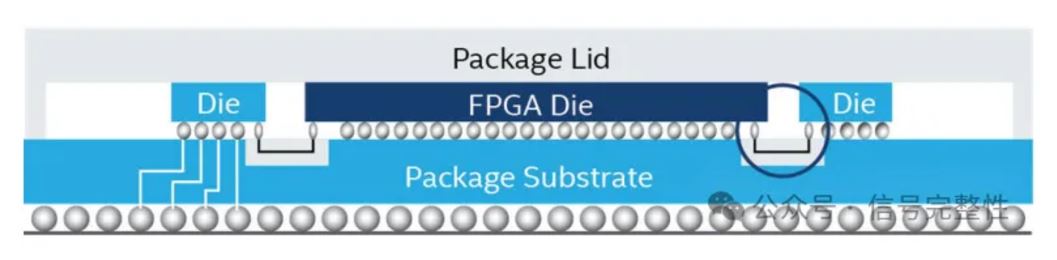

o模块化设计:支持多个Chiplet的模块化组合,使得SoC设计更加灵活。常与Intel的 EMIB(Embedded Multi-die Interconnect Bridge) 技术配合使用。

优势:低功耗、高带宽、开放性好。

典型应用:HPC、加速器芯片、ASIC与FPGA集成、网络处理器。

4. CXL (Compute Express Link)

背景:以PCIe为基础扩展的高速互连协议。

特点:

o支持Chiplet间的高带宽互连。

o支持内存共享和缓存一致性(支持大规模并行计算)。

o可作为UCIe标准协议的一部分实现。

优势:对于需要多级存储系统的应用具有强大优势。

典型应用:内存扩展芯片、数据中心计算单元。

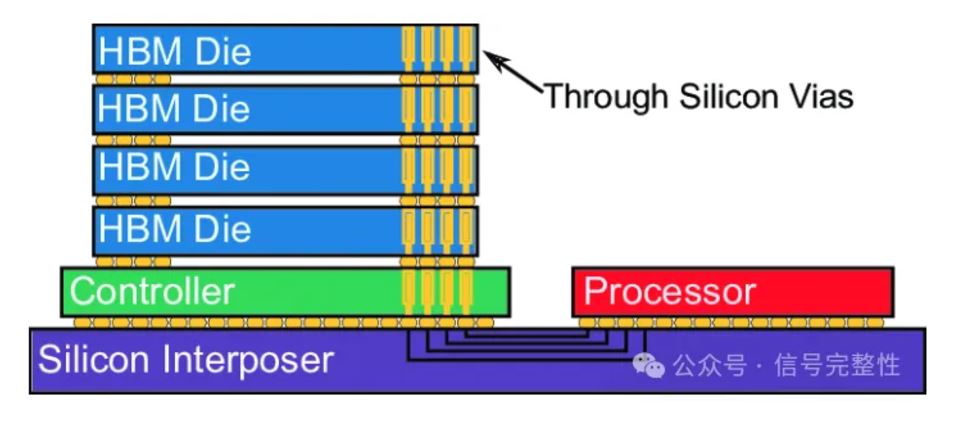

5. HBM (High Bandwidth Memory) 接口协议

背景:随着现代计算领域中高性能需求的持续增长,传统的内存技术逐渐面临带宽和功耗方面的瓶颈,尤其是在以下场景中挑战尤为突出。为了应对这些挑战,HBM技术应运而生,由JEDEC提出并发展,旨在提供高带宽、低延迟和高能效的存储解决方案。其核心思想是通过3D堆叠和Interposer实现芯片间的紧密连接,从而显著提升数据吞吐能力。

特点:

o直接通过垂直TSV连接处理器和高带宽存储器。

o提供极高的带宽和低延迟,适合数据密集型应用。

优势:带宽大,功耗低。

典型应用:AI加速器、GPU与HBM内存的互连。

6. PCIe (Peripheral Component Interconnect Express)

背景:Chiplet还有一种通用互连方式就是PCIe,这在早期广泛使用,由于PCIe的一些固有的问题,比如延迟较大,所以后来就被UCIe取代了。

特点:

o支持较长距离和多模块互连。

o延迟相对较高,不如UCIe等新标准高效。

优势:通用性强,生态成熟。

典型应用:服务器、多芯片的互联。

7. Proprietary Protocols (专有协议)

一些公司为满足特定需求开发了一些定制的互连协议,但是专有协议相对来讲都是比较封闭的,有的时候很能形成一个好的生态。

AMD Infinity Fabric:

o用于AMD的CPU、GPU之间的高效互连。

o支持芯片模块化扩展,功耗优化良好。

Intel EMIB (Embedded Multi-die Interconnect Bridge):

oIntel专有的封装互连技术,提供高密度、短延迟连接。

NVIDIA NVLink:

o专注于GPU之间或GPU与CPU之间的高带宽互连。

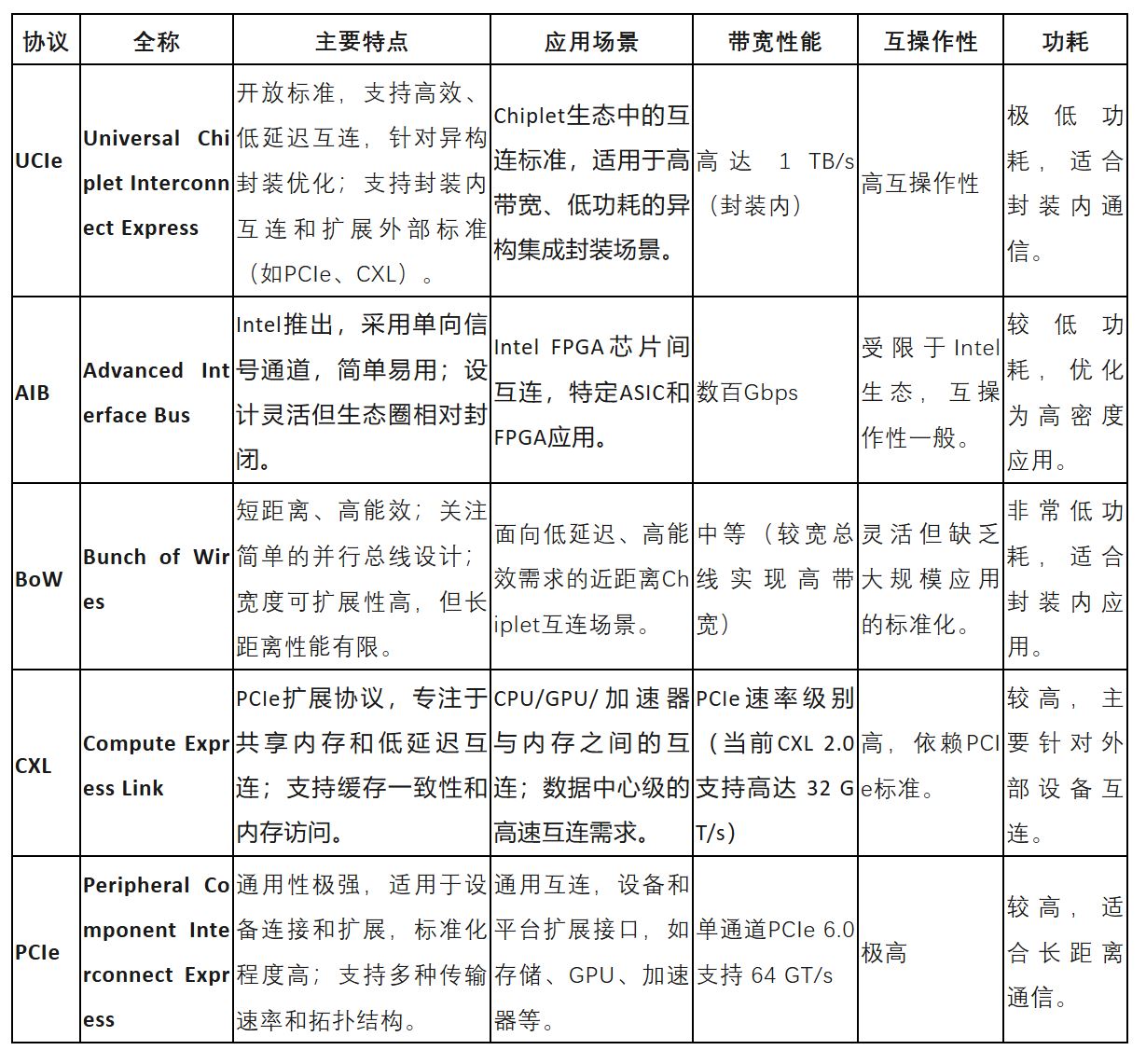

以下是对 UCIe, AIB, BoW, CXL, 和 PCIe 的主要特性和应用场景的对比:

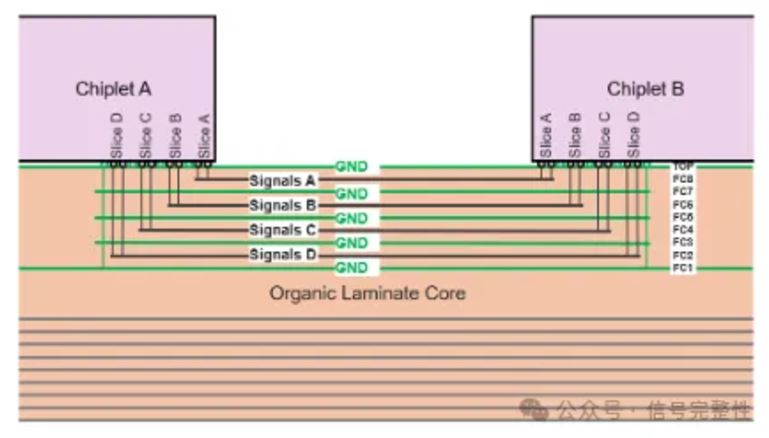

Chiplet的信号完整性挑战与仿真

以UCIe为例,信号速率非常高,单通道的传输速率最高可达32Gbps;在单位面积上的信号网络特别多;误码率也要求非常严苛,等等。

所以,当通过先进的封装方式实现多个芯片模块的高效互时,就会带来明显的信号完整性挑战,包括串扰和损耗、Skew、寄生效应、电源完整性和、热-电耦合以及严苛的误码率问题。

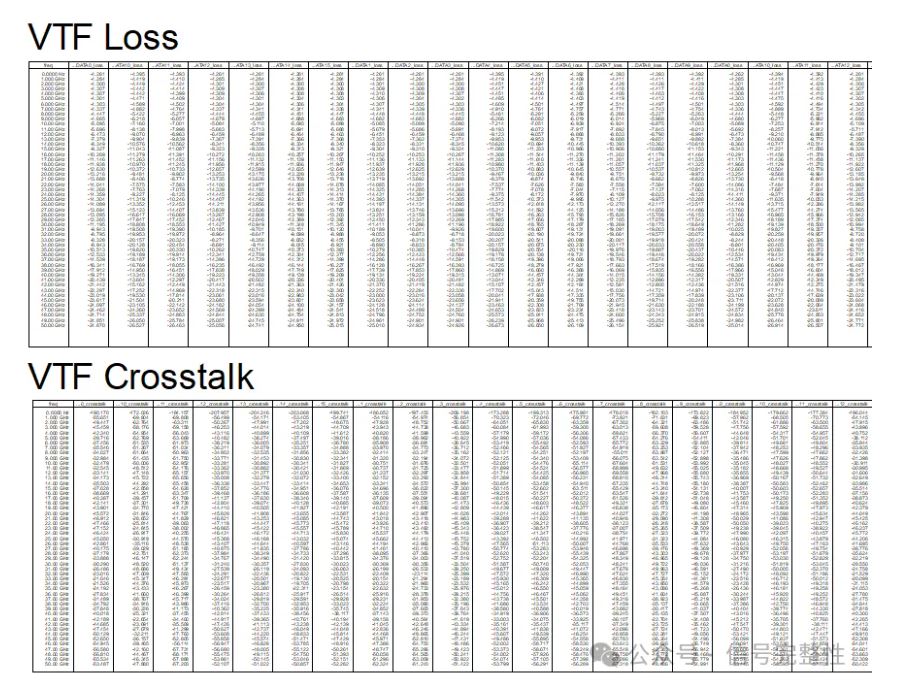

如何进行Chiplet的信号完整性仿真,也有非常大的挑战。Chiplet高速信号完整性仿真兼具了SerDes和DDR总线的仿真特点,比如信号速率高、误码率要求严苛(有的需要1e-27)、信号线多、单端信号线传输、需要单端的IBIS-AMI模型、需要仿真VTF等等。

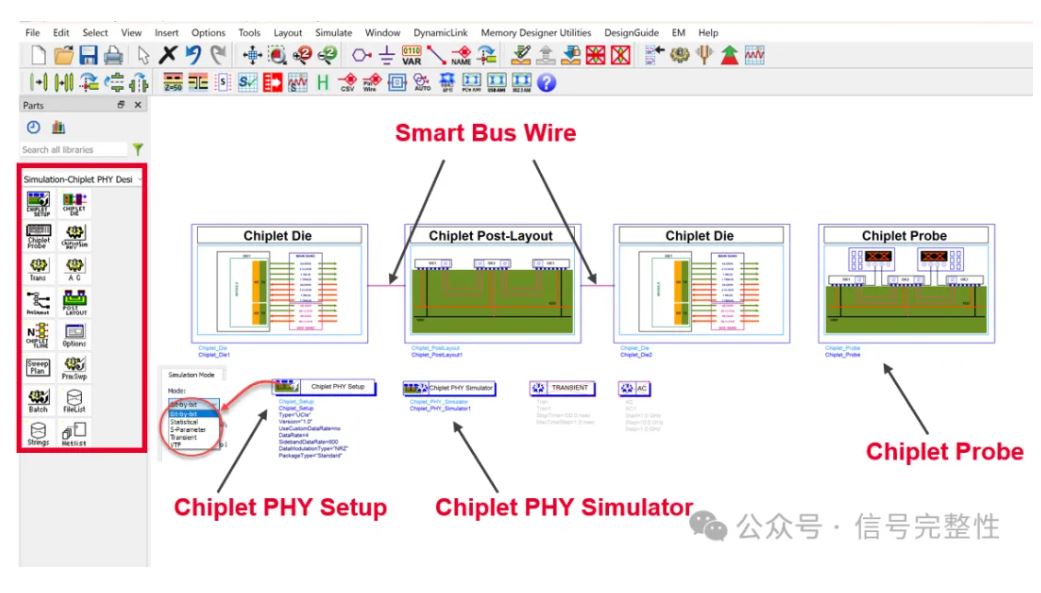

当前,我们主要采用的是ADS Chiplet PHY Designer和EMPro进行Chiplet的信号完整性仿真。通过ADS或者EMPro提取封装的S参数。

根据封装类型、协议类型等要求,在ADS中建立仿真拓扑结构,如下图所示:

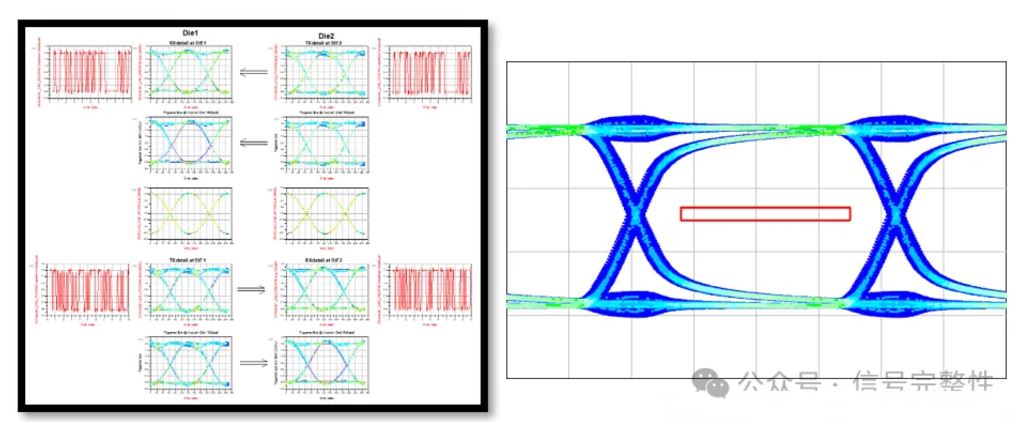

可以仿真获得眼图、误码率以及VTF等指标结果,如下所示为眼图结果:

如下图所示为VTF结果:

总之,随着UCIe正成为行业主流,但是为特定性能需求(如低功耗或高性价比)而设计的专有协议(如BoW或HMB)也仍有市场。长期来看,UCIe有望整合其他协议(如CXL)形成更广泛的生态。通过选择合适的互连协议,可以根据Chiplet的具体应用场景实现带宽、延迟、功耗之间的最佳平衡。

封装内互连:UCIe 和 BoW 更加适合,其中 UCIe 支持多协议扩展,是未来的开放标准;BoW则偏向高能效、简单实现的应用。

芯片间互连:AIB 提供了一种更定制化的方式,但受限于Intel生态;CXL 和 PCIe 则提供了长距离通信的强大功能,其中 CXL 增强了缓存一致性能力。

生态兼容性:UCIe 和 PCIe/CXL 在开放性和标准化支持上表现优异,推动了更广泛的应用。

不论是哪一种互连总线协议,信号完整性的设计和仿真也会遇到越来越多的挑战。