11 RFSoC SDR的设计工具和工作流程

11.7 天线,滤波器和放大器

当使用RFSoC进行原型设计时,通常需要外部无线电组件。例如,可能需要天线来改善信号采集,或者需要外部滤波器来抑制频谱混叠。我们的讨论将围绕简单、易于构建的前端设计展开,不包括外部设备的专门设计。最后,我们将只关注信号采集设备。

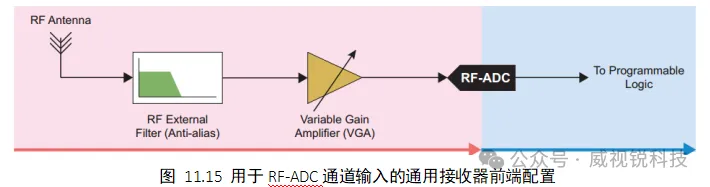

图11.15展示了RF-ADC的简单前端配置。天线用于采集信号,外部滤波器抑制不需要的频带,放大器通过将信号的功率增加到所需的水平来改善信号采集。

1.天线

在RF-ADC的输入端增加天线将显著改善信号采集。有许多商用现货(COTS)天线对无线电频谱的一般探索很有用。推荐使用以下天线:

被称为NooElec™NaTLSnake的宽带天线束有几个天线,在100MHz和1800MHz之间的几个频率上工作。

有一种应用特定的天线,称为Linx Technologies™的ANT-2.4-LCW-SMA[232],适用于Wi-Fi,蓝牙和ZigBee通信标准。

无源天线和有源天线是可用的:无源天线不放大获取的信号,而有源天线包括一个集成放大器,增加信号的功率。上面突出显示的两个天线都是无源的。在选择天线时应小心谨慎,特别是在涉及有源天线的情况下,并确保在额定值内运行,以避免对RFSoC造成损害。

2.放大器

可能有必要在RFSoC平台的前端添加少量放大以获取适当功率的无线电信号。添加放大器是不完全必要的原型无线电设计。我们建议只有在绝对需要的情况下才添加放大器。以下通用放大器是有用的:

NooElec VeGA Barebones -超低噪声可变增益放大器(VGA)模块。

noelec LaNA -宽带超低噪声放大器(LNA)模块。

请注意,过度的信号放大可能会损坏您的RFSoC平台。应始终注意确保RF-ADC输入获取的信号功率在适当范围内。

3.外部过滤

有一系列外部滤波器可以应用于RF ADC通道的输入,以改善信号采集和抑制频谱混叠。滤波要求是根据您想要检查的频带来确定的。我们的建议如下:

迷你电路®VLF-1800+低通滤波器,检查频率高达1800MHz。

有许多滤波器可用于特定应用和无线标准。例如,Mini-Circuits VBF-2435+带通滤波器适用于获取Wi-Fi信号。

与天线类似,有源滤波器可以增加信号电压,而无源滤波器则不能。因此,如果将有源滤波器的输出连接到RFSoC,则应注意。这里突出显示的两个示例过滤器都是被动类型。

11.8 RFSoC上PYNQ的SDR设计流程

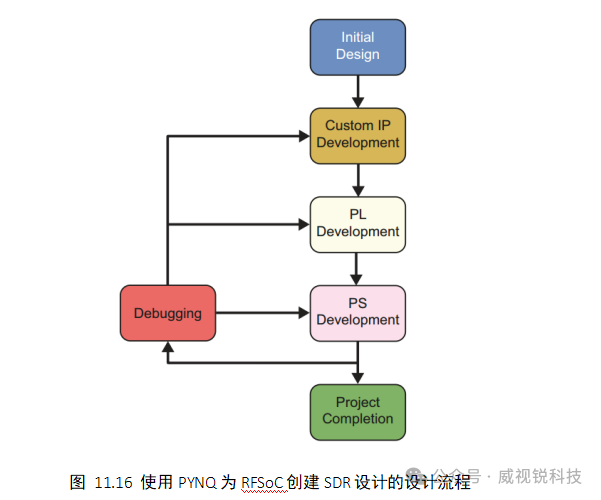

本节中详细介绍的设计过程可以分为六个独立的步骤,如图11.16所示,并在接下来的几页中进行讨论。

11.8.1 初始设计过程

在这里,系统设计人员必须考虑许多因素,例如RFDC接收和/或发送的频率范围,以及这些信号的带宽。这一步也应该使用频率规划,以确定所需的配置是否会导致任何带内干扰。这些因素将决定在设计中使用所需的采样率和时钟率。例如,如果信号带宽远小于RFDC所需的采样率,则可以使用插值或抽取级来降低PL上的时钟速率。然而,如果需要大带宽,则可能需要使用SSR来满足PL时间限制。

另一个需要考虑的因素是FPGA上IP之间的通信,以及PL和PS之间的通信。Vivado中提供的许多IP都是兼容AXI的,因此对于任何自定义IP也采用兼容AXI的接口往往是有益的。如果要在PS和PL之间传递大量数据,则可能需要AXI流 DMA,而对于低带宽信号,AXI - Lite接口通常就足够了。

在这个阶段考虑如何构建PS软件以及如何与PL硬件交互是很重要的。AMD为其IP提供了许多可以从PS控制的驱动程序,例如AXI DMA。如果要开发自定义IP,那么可能还需要为它们开发自定义驱动程序。

此外,如果设计需要使用AXI - Lite控制信号,那么PL硬件必须符合AXI - Lite标准并适当地处理它们。

11.8.2 定制IP的开发

下一步是开发和测试在FPGA上运行的定制IP。作者在这个阶段的首选工具是模型编写器和HDL编码器,两者都在MATLAB/Simulink环境中运行。使用Simulink使系统设计人员能够在将IP功能集成到Vivado设计之前快速模拟和测试IP功能,例如,可以利用Simulink源块为仿真提供适当的刺激,并且可以使用Sink块来可视化时间和频域的结果。这两个工具都能够在它们生成的IP中合并符合AXI的端口。

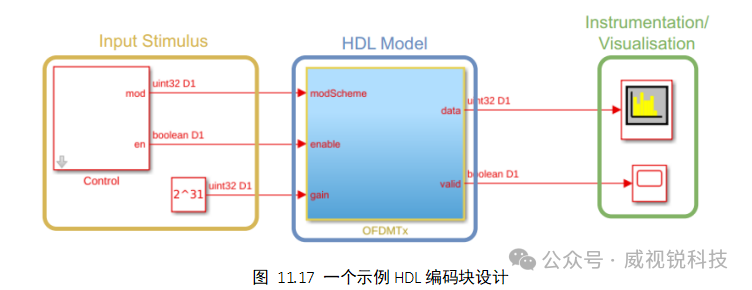

如图11.17所示为HDL Coder设计示例,突出显示了构成IP核的HDL模型,以及输入刺激的生成和输出信号的检测。

Simulink中的时钟使用采样时间(换句话说,采样周期)的概念,这是采样率的倒数。因此,采样时间参数是指IP所需的时钟速率。

一般情况下,单个时钟驱动IP的所有接口,设置为匹配所需的采样率。如果在自定义IP中需要任何速率更改,那么必须注意IP必须由以最高采样率运行的时钟驱动,这一点很重要。然后,这些工具在IP内生成其他时钟,以驱动以较低采样率运行的块;所需的采样率(以及时钟速率)通常与整数因子相关。

在设计定制IP时,重要的是要考虑输入和输出,以及它们如何与更广泛的设计交互。如前所述,使用AXI标准是值得考虑的,它将允许这些IP与Vivado中其他兼容AXI的IP很好地协同工作。AXI流可用于通过处理链传递RF数据,而AXI- Lite可用于控制信号,例如启用和复位。

Simulink提供信号范围和频谱分析仪工具,允许系统设计人员在将模型转换为HDL IP之前测试和验证模型的功能。频谱分析仪对于确定信号数据是否被正确处理非常有用,而信号范围可用于识别轴流接口信号的问题。

11.8.3 自定义IP集成到Vivado,硬件系统设计

一旦开发和测试了自定义IP,就可以将它们导入到Vivado并集成到完整的PL设计中。这一步可能是最关键的,因为它要求系统设计人员对底层硬件及其功能有很好的理解。在Vivado中,系统设计人员将MATLAB/Simulink中设计的自定义IP与RF数据转换器等其他IP之间的接口连接起来;以及PL和PS之间的任何沟通。

此外,这是在设计中设置时钟速率和采样速率的地方。必须小心确保每个IP都由正确的时钟驱动,否则可能会出现意外行为,并且难以调试。本书中的大多数设计都是从三个独立的时钟源运行的:(i) PL时钟,用于驱动AXI- Lite接口;(ii) DAC时钟,驱动与传输路径相关的IP;(iii) ADC时钟,它驱动接收路径上的ip。在某些情况下,可能需要使用时钟转换器来生成ip所需的频率。

创建PL设计的最直接方法,也是作者所采用的方法,是使用Vivado的内置IP Integrator工具。IP集成商允许系统设计人员使用可视化的、基于块的方法将IP连接在一起。

硬件系统设计人员最终会遇到的一个问题是时序关闭,即确保设计能够支持所需的时钟速率。对于SDR设计,这可能涉及在接收器的信号处理链中较早地抽取信号,或者相反,在发射器的信号处理链中较晚地插值。另一个选择是更改Vivado中的实现策略,它定义了放置和路由的方法。Vivado定义了许多不同的策略,包括一些主要关注定时关闭的策略(通常具有延长的运行时间,但有可能获得更好的结果)。

11.8.4 PS软件的开发

在PL设计完成后,就可以开发PS的软件了。从本书中的各种设计中可以明显看出,PYNQ是作者在PS上开发软件的首选框架。使用PYNQ有许多好处,包括对标准IP的良好驱动程序支持,以及为自定义ip创建驱动程序的简单方法。使用Python还可以快速有效地编写代码,从而相对快速地识别PL和PS上的任何问题。此外,Python生态系统包含无数已建立的库,例如Plotly和SciPy,这使得直接在PS上开发用于可视化和分析信号的代码变得简单。

由于其易用性,PYNQ提供了一种快速的方法来确认PL设计是否按预期执行。AXI - Lite寄存器可以使用MMIO库进行读写,RFDC驱动程序可用于配置RF数据转换器,DMA驱动程序使通过共享内存在PS和PL之间传递数据变得简单。如果数据仅在PL和RFDC之间传递,则可能需要在PL上运行集成逻辑分析仪(ILAs)或外部设备(如频谱分析仪和/或信号发生器)来验证发送和接收路径的功能。

11.8.5 调试

正如调试过程中常见的那样,解决方案通常很简单,但是确定故障的位置可能非常耗时。帮助这个过程的一个有用工具是Python调试器PDB,它允许用户设置断点并有条不紊地逐步执行PS代码。一旦发现并修复了错误,就可以从项目中删除调试器代码。

如果确认PS软件按预期运行,则可能需要重新访问PL设计阶段以解决问题。根据PL设计的大小,生成一个新的比特流可能需要很长时间,因此,PL调试可能是一个耗时的过程,特别是如果需要多次重新生成比特流,以尝试不同的解决方案。出于这个原因,在进入软件开发阶段之前,广泛地模拟和测试PL硬件是有益的。

虽然在设计中可能存在许多不同的故障,但根据我们的经验,在为RFSoC开发系统时可能会出现两个常见问题。正如本节前面所讨论的,不正确的时钟频率可能导致不可预测的行为。RFDC通常由外部时钟基础设施驱动,因此确保时钟的正确编程以及它们提供预期的频率非常重要。

另一个常见问题来自于如何在自定义IP中生成和处理AXI流信号。除了tdata信号外,AXI流IP还可以包含各种其他接口信号,包括tvalid、tready和包结束信号tlast。如果这些信号没有与tdata信号正确同步,那么沿着信号路径进一步的IP可能无法正确操作。例如,在设置数据传输时,PYNQ DMA驱动程序要求数据包大小具有特定的长度。如果最后一个信号脉冲太早或太晚,指示数据包的结束,这将导致DMA挂起。如果处理不当,trready信号也会出现类似的问题。

11.8.6 项目完成

一旦PS和PL被验证工作如预期,软件就可以形式化。这可能包括为自定义IP制作驱动程序,或者(如果适合预期用例)创建刺激或可视化工具,例如本书中的许多设计。在这些设计中广泛使用的另一种可能性是,将大部分功能抽象为类和函数,然后将它们导入到Notebook中。这使得Jupyter Notebook中的代码更加精简,更容易理解。

文章来源:威视锐科技