作者:Wang Yushan,AMD工程师;来源:AMD开发者社区

引言

在 Zynq UltraScale+ MPSoC 平台上,DDR 是多个主设备(A53、R5、PL)共享的关键资源。在复杂的实际系统中,DDR 通常同时承载操作系统、应用程序以及高速数据通道的访问需求,传统的软件分析往往无法精确评估 DDR 带宽占用情况。因此,本文提出了一种基于 PS的AXI 性能监视器(APM)在 ZCU102 开发板上实现的硬件级 PS内部DDR 带宽监控解决方案。

核心思路如下:

• A53 / AXI Traffic Gen 产生可控的 DDR 访问流量

• R5_1 核心通过 APM 监控 DDR 带宽

• 每秒通过 UART1 打印端口 S1~S5 的读写带宽

系统架构

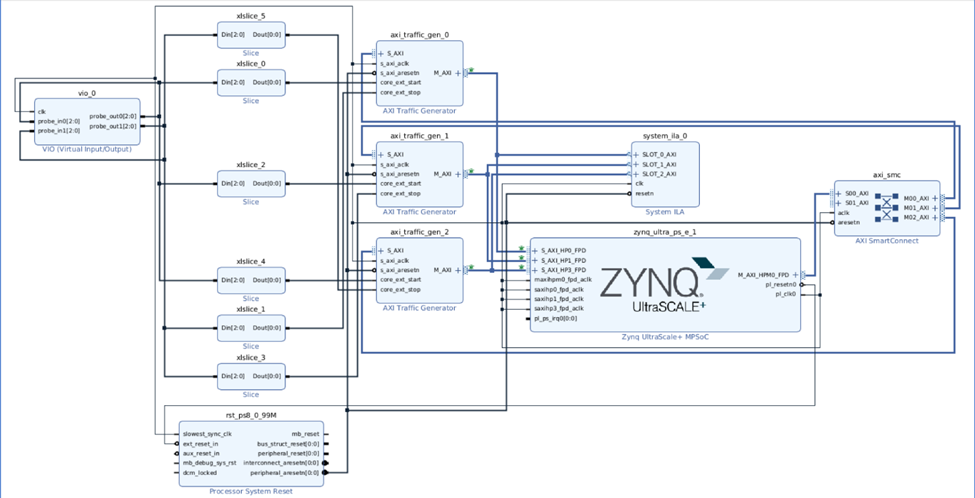

1.Block design设计

AXI Traffic Gen: 生成连续、可控的AXI读写数据流

APM: 监测AXI总线行为并统计性能指标

VIO: 控制AXI Traffic Gen流量的生成和停止

ILA: 观察AXI Traffic Gen流量的生成情况

2.APM配置说明

AXI Performance Monitor 通过 Slot 的方式监测不同的 AXI 通道。每一个 Slot 对应一条 AXI 接口,本实验中 Slot 与 DDR 高速端口(HP Port)的映射关系如下:

Slot1 - M_AXI_HPM0_FPD

Slot2 - M_AXI_HPM0_FPD

Slot3 - S_AXI_HP0_FPD

Slot4 - S_AXI_HP1_FPD

Slot5 - S_AXI_HP3_FPD

有关AXI Performance Monitor(APM)的更多信息,可以参考以下文档:

软件实现

1. A53侧

A53 侧主要用于生成 DDR 访问负载,其功能可以非常简单,例如:

向 DDR 指定地址范围持续写入数据

再从同一地址区间回读数据形成读写负载

在实际应用中,该程序可以替换为真实业务负载,以更贴近真实系统场景。

2. R5侧: APM带宽监测

R5_1 核心运行裸机(standalone)程序,主要完成以下任务:

初始化 APM

配置 Slot 和 Metric(Read / Write Byte),每 1 秒采样一次

若要改变采样频率,可通过调整sleep(MONITOR_INTERVAL_S)函数中的MONITOR_INTERVAL_S参数实现。

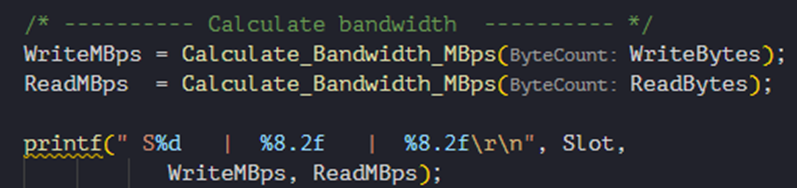

计算并打印带宽

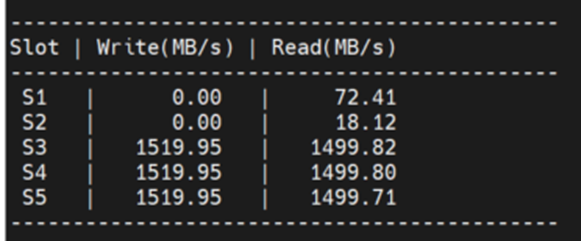

3. 串口输出示例

串口终端将周期性输出类似如下的信息:

运行和调试

1. Vivado工程:

在2024.2 Vivado中创建一个新工程。

运行附件的tcl脚本APM_PS_test.tcl创建Block Design(BD)工程。

右键点击BD,选择“Create HDL Wrapper”。

点击“Generate Bitstream”生成bit文件。

选择菜单File->Export->Export Hardware导出xsa文件。

2. Vitis工程:

打开2024.2 Vitis,使用导出的xsa文件创建platform project,选择R5-1的standalone OS。

创建一个空的application project,导入附件的xaxipmon_ocm_example.c,然后编译。

在platform->settings->vitis-comp.json->左上角add domain/BSP,添加一个新的A53的standalone OS。

创建一个空的application project,导入附件的helloworld.c(也可以是自己需要监测的任务程序),然后编译。

创建System Project,将A53与R5两个application一并加入,方便统一编译与调试。

3. 下载与调试:

在Vitis中选择Flow下的Create Boot Image,生成BOOT.bin文件

将BOOT.bin文件拷贝进SD卡,并将板子以SD卡模式启动。

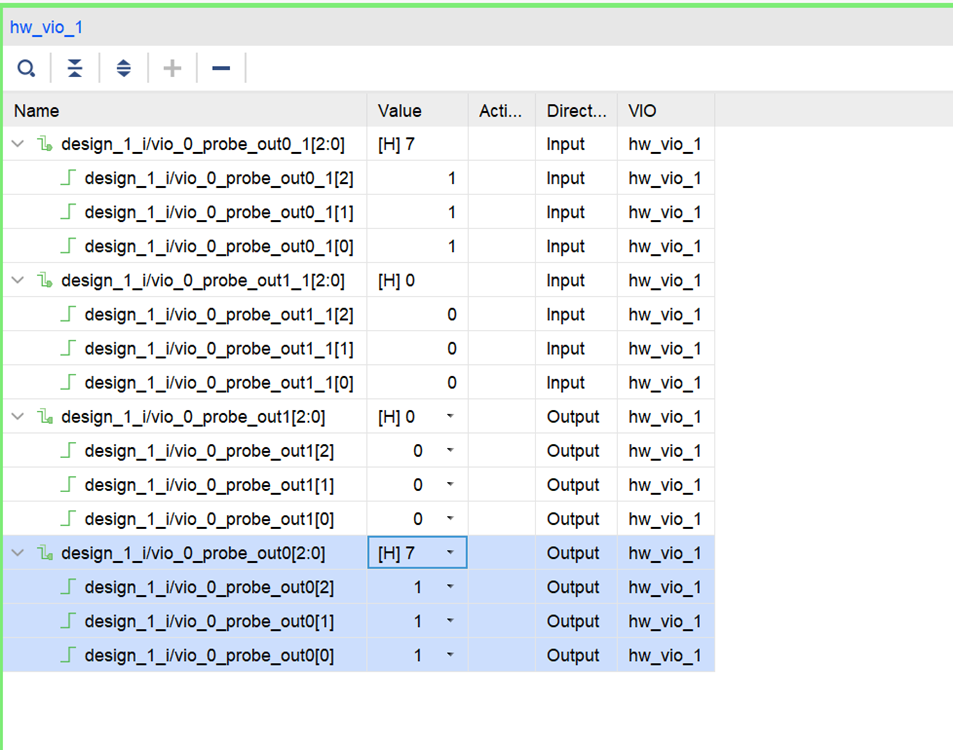

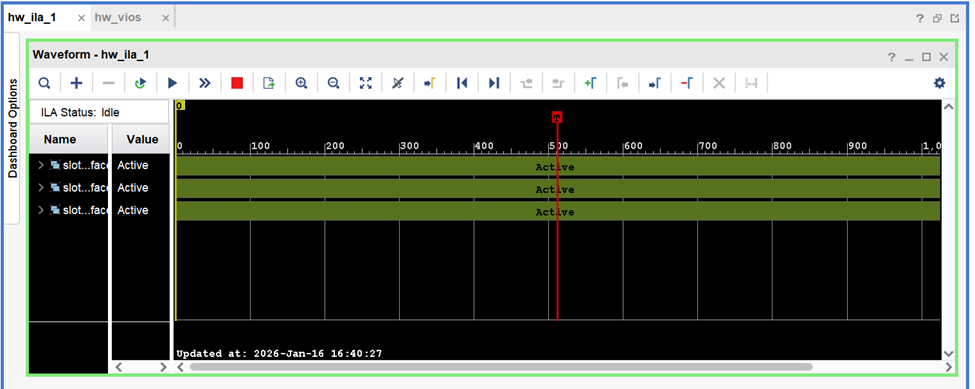

如下图,打开hw_vio_1,通过控制design_1_i/vio_0_probe_out0[2:0]的值来控制AXI Traffic Gen流量的生成和停止,并通过hw_ila_1来观察AXI Traffic Gen流量的生成情况。

回到Vitis串口终端,查看 APM 输出的 DDR 带宽统计结果。