PCIe如何紧随计算和网络步伐?

judy 在 周二, 04/30/2024 - 10:23 提交

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图

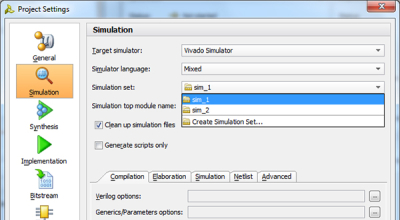

Vivado 具有一个功能特性,能够将这些文件便利地排列组合为多个可轻松访问的不同仿真集。本文描述了如何在 Vivado 中使用多个仿真集。

本文介绍Xilinx SelectIO资源内部IDELAYE2资源应用

本文主要讨论一下如何在外部数据文件中指定RAM 初始内容。

从专用串行数字接口 (SDI) 的点对点连接转到面向媒体内容交换和协作的以太网 IP 网络,这一颠覆整个广播媒体制作供应链的演进趋势仍在继续

本文将深入探讨 PCIe 延迟和功耗考虑的复杂性,讨论在 HPC SoC 设计中优化这些关键方面的策略。

机器人技术可能很复杂。在这个项目中,我们看到AMD Kria™ KR260套件可以使用ROS 2快速开发机器人解决方案

智多晶应用团队的一项Precise_PWM demo,使用智多晶FPGA将PWM控制精度从FPGA应用常见的10ns~5ns的水平提升到了1ns的脉宽和相位精度,精准可控,且资源消耗极低。

本文记录描述了如何在仿真集内选择不同的顶层模块。

本章使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性