Vivado的五种仿真模式和区别

wyh102 在 周日, 04/23/2023 - 01:07 提交

本文介绍vivado 的仿真模式

本文介绍vivado 的仿真模式

本文旨在呈现使用 DDR4、LPDDR4 或 LPDDR4X 存储器控制器的 Versal ACAP 器件的外部参考时钟电路要求

通过 IP integrator 选中多个 NoC site 时,不会在整个实现过程中遵循这些约束

本文介绍7系列FPGA使用电阻网络实现MIPI电平的例子

本文设计了一种基于JESD204B 的射频信号高速采集系统

当使用第三方综合器比如 Synopsys® Synplify Pro或Mentor® Graphics Precision 来综合

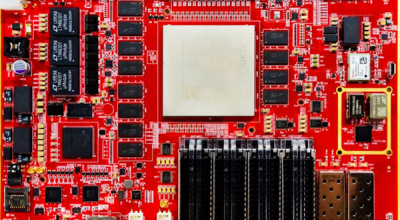

VPX 6130是一款与VPX8800配套使用的基带信号处理加速卡,可以通过PCIe X16的方式与主控卡进行通信

本文介绍一下使用FPGA实现低延迟的成像系统

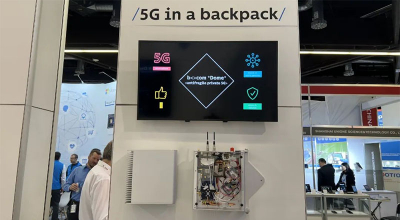

与Patrick Savelli一起看看这项允许在特定情况下部署私人5G网络的技术

从音频输入到输出,现有的实时数字音频系统很难实现低于 1ms 的时延