FPGA设计基础——数据同步

judy 在 周三, 08/03/2022 - 10:07 提交

数据同步一般是指数据从不同时钟域之间传递的过程,是FPGA设计中的基础。数据同步中最常见的问题就是数据在同步过程中被改变

数据同步一般是指数据从不同时钟域之间传递的过程,是FPGA设计中的基础。数据同步中最常见的问题就是数据在同步过程中被改变

在设计代码的时候,大部分人都是习惯于使用外部的编辑器进行设计,而不是使用vivado自带的编辑器

本文主要着重介绍了两个方面:如何从源码工程构建编译生成镜像文件和如何快速运行demo工程。

本视频演示如何开始使用在 VMAccel FPGA 云上的 VCK5000 Aupera 视频机器学习流媒体服务器解决方案 2.0。

通常对FPGA下载程序时,会采用JTAG口下载,完成好HDL设计,并且验证无误后,对设计文件进行综合,布局布线以及生成比特流文件

作为FPGA工程师,我们无法保证所有设计都不出现负数或者小数的情况,今天就为大家分享一下FPGA中负数与小数的表达。

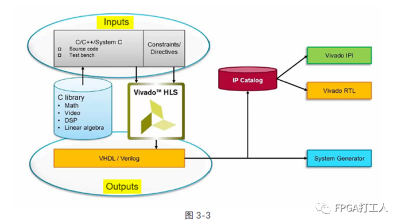

HLS现在应该算是比较成熟了,其最大的吸引力就是可以采用纯C/C++或者System C来对FPGA进行编程,相对于VHDL和Verilog更加容易上手

5G新无线电(NR)网络的设计目的是与现有网络实现多年共存。在世界各地,营运商已投资数十亿美元建设2G/3G/4G网络,用于无线电设备和选址

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点

首先新建ddr的IP,具体每个参数的含义,可以参考之前写的《Virtex7 Microblaze下DDR3测试再右键》,打开IP的Example Design