一天上手Aurora 8B/10B IP核(3)----时钟、复位与状态指示

judy 在 周二, 04/19/2022 - 14:27 提交

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?

Vitis 嵌入式平台创建所需要注意的问题

当运行一个基于DPU的应用程序时,当平台中的DPU和编译后的XMODEL之间存在架构不匹配时,就会发生指纹错误。

本文介绍Vivado IP Integrator中实现DFX(Dynamic Function eXchange)的快速入门

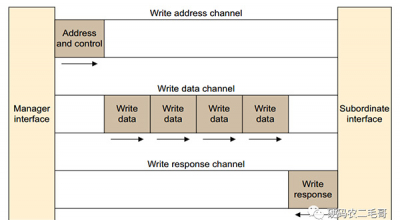

在zynq开发过程中,AXI总线经常遇到,每次看到AXI总线相关的信号时都一头雾水,仔细研究一下,将信号分分类,发现其实也不难。

我们前面的两篇文章讲了7系列的时钟结构和clock region内部具体组成,这篇文章我们来讨论下MRCC和SRCC的区别。

本教程对应目标为 Versal ACAP VCK190 和 VMK 180 评估板。本教程中的示例已使用 VCK190 ES1 评估板经过测试。要使用本教程,您需要具备以下硬件项,这些硬件项均随附于该评估板中

我用的硬件板卡是ZCU102,从Vitis AI的AI-Model-Zoo中下载了pt_unet_chaos-CT_512_512_23.3G_2.0模型的ZCU102文件,解压后发现只有编译好的.xmodel文件

使用在 ULTRA96V2 上运行的深度神经网络在 LiDAR 点云中进行 3D 对象检测的端到端演示。

零知识密码学是计算机科学领域在近 50 年间最引人注目的创新之一。零知识证明的一系列先天优势使其成为了各种区块链扩容和隐私解决方案的重要组成部分