Versal PCIe Example Design 仿真技巧(1)

judy 在 周三, 06/08/2022 - 10:05 提交

PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型

PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型

远程调试在整机调试时是很有必要和方便的,今天带给大家一个通过无线wifi下载调试fpga的一种方法

在工业应用中传输信息可能具有挑战性。在这个项目中,让我们看看我们如何使用 FPGA 和 RS485 做到这一点。

考虑到很多客户对于FPGA的基础知识掌握不够扎实,也不是每个客户的悟性都非常高,所以准备在原来的FPGA基础入门10个课时基础上再增加一些demo,给大家FPGA学习使用。

AMD将HPC基金与Xilinx异构加速计算集群(HACC)计划相结合,增加7 Petaflops超级计算机容量以推动突破性研究

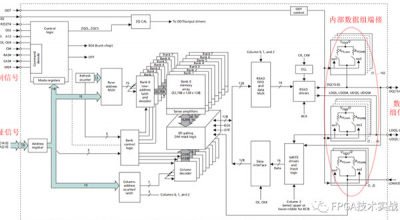

本文我们介绍下DDR3的基础知识,涉及DDR3管脚信号、容量计算、重要参数介绍内容

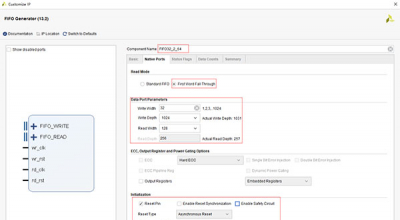

Xilinx系列FPGA,包含两种RAM:Block RAM和分布式RAM(Distributed RAM),他们的区别在于,Block RAM是内嵌专用的RAM,而Distributed RAM需要消耗珍贵的逻辑资源组成。

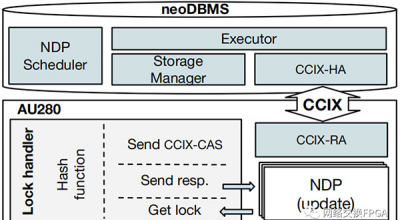

在今年的FCCM会议上,德国TU Darmstadt和Reutlingen University联合发表了一篇CCIX相关的文章,该文章使用CCIX作为FPGA与Host之间的接口,并详细评估了CCIX与PCIe之间的差异

本视频将介绍基于VCK190开发工具的ESIstream Versal开发包,帮助您熟悉其使用方法并加速您的开发流程。

本文就针对IP设计中注意事项、有用策略及FPGA原型设计等进行简要说明。