YunSDR通信小课堂-Versal AI Core专题(第42讲)

judy 在 周二, 04/29/2025 - 10:58 提交

AI Engine内存模块有32 KB的数据内存,分为八个存储体、一个内存接口、DMA和锁。传入和传出方向都有DMA,每个内存模块内都有一个Locks块

AI Engine内存模块有32 KB的数据内存,分为八个存储体、一个内存接口、DMA和锁。传入和传出方向都有DMA,每个内存模块内都有一个Locks块

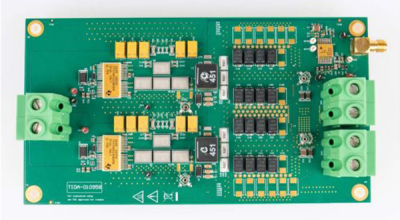

TIDA-010958 是一种面向 AMD® Versal® AI Core XQRVC1902 内核电源轨的耐辐射同步降压电源参考 设计。此设计非常适用于 12V 输入操作,可生成 0.8V 的输出电压和最大 80A 的输出电流

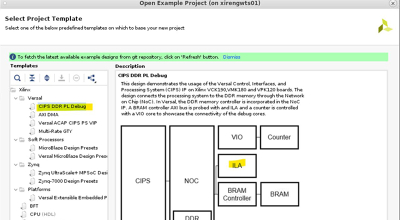

我们将使用 Clocking Wizard 文档 PG321 中的“通过 AXI4-Lite 进行动态重配置的示例”章节作为参考。

AMD Versal™自适应SoCs将标量引擎、自适应引擎和AI Engine与领先的内存和接口技术相结合,为任何应用提供强大的异构加速功能

随着系统设计人员利用新型处理器、FPGA 和 ASSP 技术,实现低功耗和高效 LVDS 链路比以往更加重要

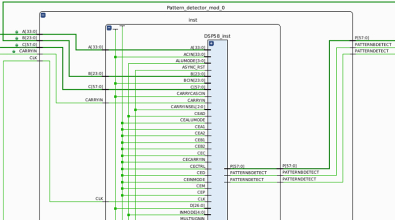

本文包含一个设计示例,该示例使用 DSP58 将中点值收敛舍入到最近的偶数和奇数。

Versal自适应SoCs将标量引擎、自适应引擎和智能引擎与前沿内存和接口技术相结合,为任何应用程序提供强大的异构加速

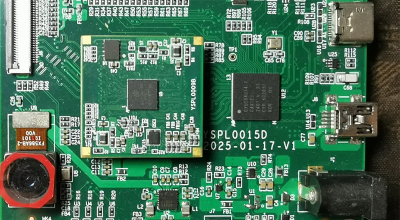

本文对FX10的器件特点、硬件设计和开发调试环境的搭建做了一个简要介绍。

本篇文章介绍了在任何平台上使用 PetaLinux 的先决条件。PetaLinux 是一种嵌入式 Linux 软件开发套件 (SDK)

本文介绍了 Altera A10 SoC HPS UART 作为数据通讯接口的应用,重点讲解了波特率配置、分频值计算及实际应用中的调试技巧