作者:Krishnpriya Sinha,AMD工程师;来源:AMD开发者社区

本篇博文包含一个设计示例,该示例使用 DSP58 将中点值收敛舍入到最近的偶数和奇数。中点的收敛舍入用例采用的是 DSP slice 分片的“pattern-detection”(模式检测)模式。

收敛舍入是 DSP 分片的模式检测功能的诸多应用之一。对于 3.5、-1.5、7、6.5 等中点值用例,可以将这些数值收敛舍入到最接近的偶数或奇数整数。

(UG193) 中的“收敛舍入:LSB 纠正技术”章节揭示了收敛舍入的 DSP48 分片配置及其背后的概念,DSP58 也适用类似的配置和概念。

除 DSP 分片外,该功能还需要使用互连结构。本篇博文完整呈现了使用 DSP 分片和互连结构进行 LSB 纠正收敛舍入的完整设计。

设计方面

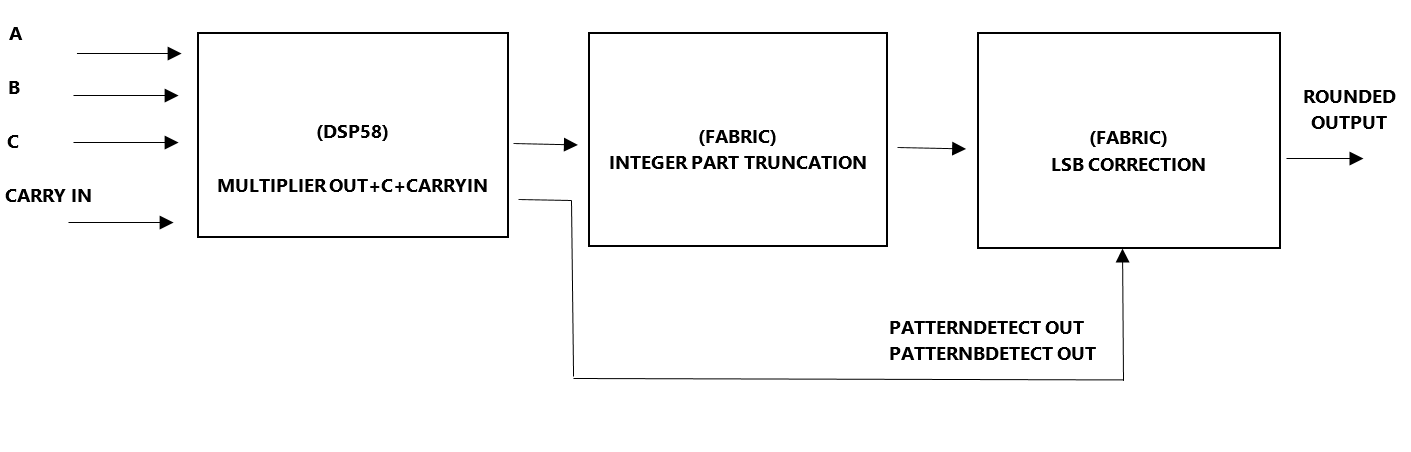

图 1 采用 LSB 纠正技术的收敛舍入概念性模块框图。

图 1 采用 LSB 纠正技术的收敛舍入概念性模块框图。

如图 1 所示,该设计示例的概念框图分为三个模块。

第一个模块使用 DSP58 例化语言模板,在 DSP58 内执行,DSP58 会执行 A*B 并将乘积与输入 C 和 CARRYIN 相加。乘法输出 P 即为目标中点值,需舍入到最接近的偶数/奇数整数。输入 C 表示中点值的小数位宽,计算方法为其值中所含的 1 的个数加 1,即,如果 C=00000111,中点值的小数位宽为 3+1=4。CARRYIN 设置为 1 时启用偶数舍入,设置为 0 时启用奇数舍入。

DSP58 取 A、B、C 和 CARRYIN 作为输入,执行 P =(A*B)+C+CARRYIN 并将其作为输出 P 发送给下一个模块。具体方法是将 DSP58 的 OPMODE 属性设置为 000110101。除了判定中点值的小数位宽外,输入 C 还会判定要与 P 比较的模式的掩码位。基础模式全为 0,掩码位等于“C 左移 1 位”。具体方法是针对 SEL_ROUNDING_MASK 属性选择 MODE1。

如果 P 的模式类似 xx...xxxx.000...00,则 PATTERNDETECT (PD) 会变为 HIGH 高电平;如果类似 xx...xxxx.1111...11,则 PATTERNBDETECT(PBD) 变为 HIGH。

第二个模块会利用互连结构资源对 P 的整数部分执行截位。此模块会计算输入值 C 中 1 的数量,并判定小数位宽。知晓此位宽后,会丢弃小数位并抽取整数部分来将 P 截断。

第三个模块会对 P 的整数部分 (P_int) 进行 LSB 纠正,这整数部分即第二个模块的输出。当 CARRYIN=1 时,即,舍入到最接近的偶数整数,则会强制将 P_int 的 LSB 设为 0。当 CARRYIN=0 时,即,舍入到最接近的奇数整数,则会强制将 P_int 的 LSB 设为 1。以下真值表可帮助我们在互连结构中达成此功能:

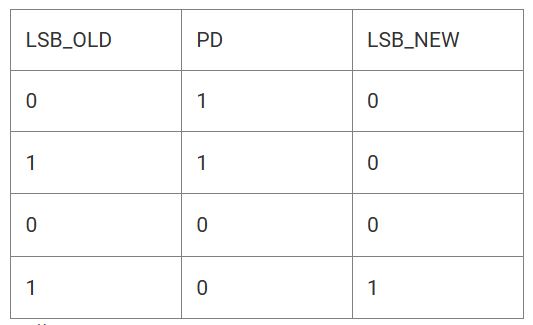

当 CARRYIN=1 时,舍入到最接近的偶数整数:

因此,LSB_NEW=(LSB_OLD) & (~(PD) )

求解后可得 LSB_NEW= ~(~(LSB_OLD) | PD )

当 CARRYIN=0 时,舍入到最接近的奇数整数:

因此,LSB_NEW= (~(LSB_OLD) & PBD) | (LSB_OLD & PBD) | (LSB_OLD & (~PBD) )

简化后可得 LSB_NEW=(LSB_OLD | PBD)

当数值并非中点值时,PB 和 PBD 都不会转至 HIGH,因此不执行 LSB 纠正。因此,该技巧仅适用于中点值。

根据上述两个针对 P_int 的新 LSB 的布尔方程,LSB 纠正的执行方式是将旧的 LSB 替换为新的 LSB,并将中点值舍入到最接近的偶数/奇数整数。

设计示例

Vivado 版本:2024.2

器件:xcvc1902-vsva2197-2MP-e-S

图 2:Vivado 中完整设计示例的模块框图。

图 2:Vivado 中完整设计示例的模块框图。

图 2 提供了将中点值收敛舍入到最接近的偶数/奇数整数的完整设计模块框图。来自 Clocking wizard IP 的 100 MHz 时钟输出驱动整个流程链中的其他 IP。VIO 用于在运行期间驱动内部 FPGA 信号。如上所述,第一个模块名为“Pattern_detector_module”,用于对 DSP58 执行运算。第二个模块名为“Truncated_Integerpart”,它将来自前一个模块输出的整数部分截断。第三个模块名为“LSB_correction”,它会执行 LSB 纠正,并提供舍入后的最终输出。

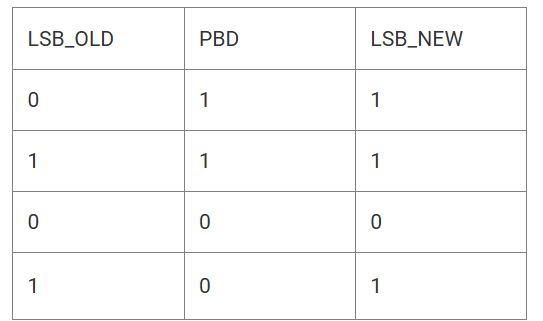

图 3 显示了 Pattern_detector_module 的综合后设计。该模块在“pattern-detection”(模式检测)模式下使用 DSP58,如下所示。

图 3:显示 DSP58 的使用过程的综合后原理图。

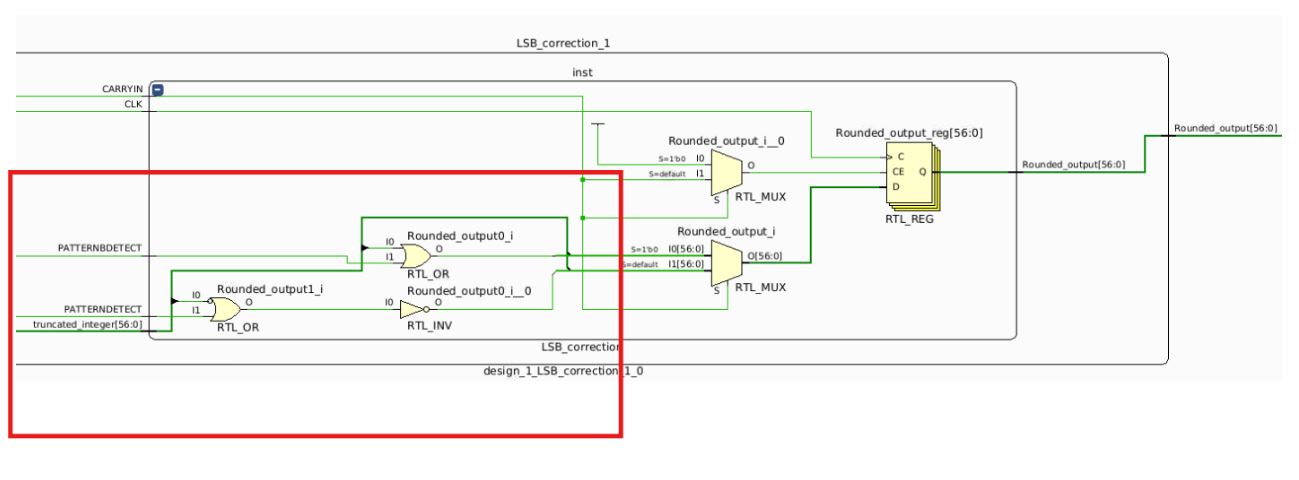

以下图 4 中 LSB_correction 模块的细化设计完全遵循前文中所得的布尔表达式。

图 4:LSB_correction 模块的细化设计。

图 4:LSB_correction 模块的细化设计。

ILA 波形图

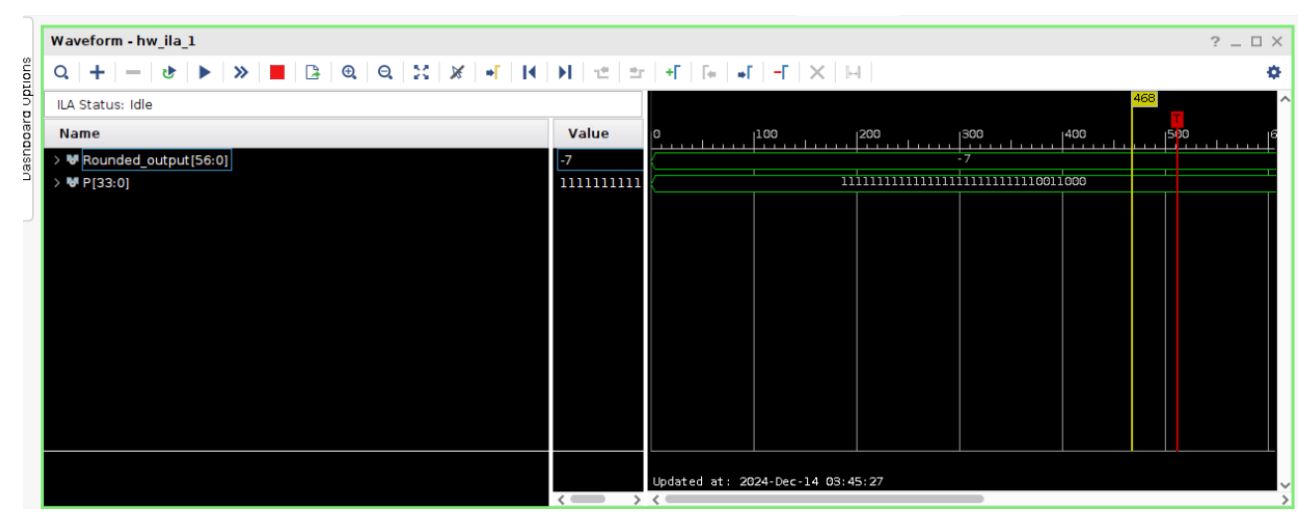

以下截屏是在 Versal AI Core (xcvc1902-vsva2197-2MP-e-S) 上运行设计时的 ILA 波形图。

测试用例 1:A= -6.5、B=1、CARRYIN=0。舍入输出为 -7。 (舍入到最接近的奇数整数)

测试用例 2:A= 4.5、B=1、CARRYIN=1。舍入输出为 4。 (舍入到最接近的偶数整数)

测试用例 2:A= 4.5、B=1、CARRYIN=1。舍入输出为 4。 (舍入到最接近的偶数整数)

优点

这种设计的优点在于,它可以利用相同的资源来执行乘法运算以及一些初始舍入步骤。

在此设计中,A*B 运算以及截位和 LSB 纠正前的部分舍入运算(例如,计算 P =(A*B)+C+CARRYIN,以及 P 的模式检测)都是仅用一个 DSP58 来执行的。

这样即可有效利用各项资源。