HLS 分区能否加速 FPGA布局布线?

judy 在 周三, 05/25/2022 - 09:46 提交

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。

本视频提供了在 MPSoC GPU 上实现 Linux 运行时电源管理的示例。

为了帮助医生更好地识别和定位病灶,厂商不断提高内窥镜的分辨率,人体医疗内窥镜的分辨率从1080P逐渐发展到如今的4K。

如何获取Xilinx FPGA的Device DNA呢,下面我从JTAG和调用源语两个方法说明,并开放核心代码供大家参考。

本视频简要介绍面向EV12AQ600/605 ADC的ADX4和ADX2 IP。

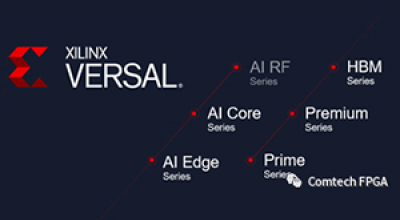

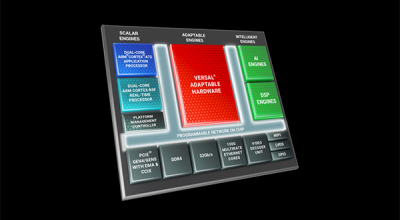

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息

本文主要介绍时钟及I/O规划的各个阶段及流程要点。

AMD收购赛灵思的目的在于将其差异化IP集成到公司未来旗下的CPU中,Xilinx无论是从丰富的计算引擎还是其AI引擎技术都能让AMD在服务器CPU市场上扩大影响力

Kria KR260 入门套件能够快速开发用于机器人和工业自动化的硬件加速应用。与基于 GPU 的解决方案相比,带来显著的生产力、单位功耗性能提升和时延下降