Vitis IDE下DUMP的功能使用简介

judy 在 周二, 04/12/2022 - 16:49 提交

在ZYNQ-7000或MPSOC的调试过程中,当我们打算通过JTAG把PL中的一些运行状态显示出来,通常会在PL中加上Debug ILA的方式来解决。

在ZYNQ-7000或MPSOC的调试过程中,当我们打算通过JTAG把PL中的一些运行状态显示出来,通常会在PL中加上Debug ILA的方式来解决。

作为赛灵思 FPGA 和自适应 SoC 上最综合全面的基于软件的 AI 加速解决方案,2.0 版本的 Vitis AI 解决方案更易于开发者使用,给边缘和数据中心带来进一步的性能提升。

本人业余搞FPGA开发的同时,还喜欢研究生产力工具,包括硬件和软件的,电脑就是重中之重,恰好今年手中有个还算比较大FPGA工程,综合一次相当费时,索性把以前记录的

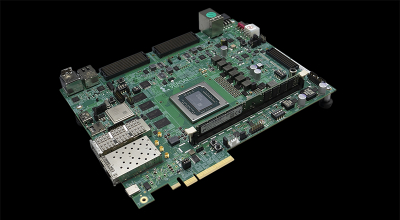

本文详细描述了ZCU670板的功能。使用本指南可以在ZCU670板上开发和评估针对Zynq® UltraScale+™ RFSoC的设计。

AMD 已为一种处理器申请了专利,该处理器具有堆叠在其 I/O 芯片 (IOD) 顶部的机器学习 (ML) 加速器。该专利表明,AMD 可能正计划构建具有集成FPGA 或基于GPU 的机器学习加速器的专用或数据中心系统级芯片 (SoC)。

使用下列脚本,可以通过JTAG实现VCK190的Linux启动。

本文对VDMA模块功能、性能、寄存器和软件编程方法进行简要介绍。

有关安全特性的示例十分广泛,从拒绝错误的用户输入、在特定条件下立即停止输入,到发出的各类警报,再到向邻近设备发出指令,不一而足。

本文将对如何生成patch以及在petalinux工具中应用patch做一个整理

将面向专门用于卷积神经网络的可编程引擎DPU,并基于边缘端MPSOC器件(以官方ZCU104平台为例),引领开发者快速搭建基于Vitis AI的DPU开发环境