Xilinx FPGA加密方案

judy 在 周一, 01/17/2022 - 16:11 提交

Xilinx 7系列采用的是AES-CBC块加密的模式,而UltraScale & UltraScale+采用的是AES-GCM流加密模式,效率更高且自带GMAC信息校验码,用以校验密文完整性。加密方式及操作上大同小异,本文仅介绍7系列和Zynq-7000裸机打包bin文件的加密方法。

Xilinx 7系列采用的是AES-CBC块加密的模式,而UltraScale & UltraScale+采用的是AES-GCM流加密模式,效率更高且自带GMAC信息校验码,用以校验密文完整性。加密方式及操作上大同小异,本文仅介绍7系列和Zynq-7000裸机打包bin文件的加密方法。

描述将 5GNR 无线电与邻近的其他高功率无线电共置一地对设计和架构选择的影响和注意事项。

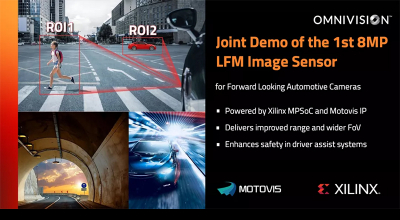

由赛灵思 MPSoC 和 Motovis IP 协助打造的 OX08B40 提供更大的检测范围和更宽的视角,让汽车驾驶辅助系统更加安全

关于傅立叶变换,无论是书本还是在网上可以很容易找到关于傅立叶变换的描述,但是大都是些故弄玄虚的文章,太过抽象,尽是一些让人看了就望而生畏的公式的罗列,让人很难能够从感性上得到理解

本文描述从 Spartan®-6 到 Spartan-7 FPGA 的迁移过程。

最近两年,Transformer在NLP、CV领域都取得了非常好的成绩。结合相关文章,Transformer的底层也是矩阵运算。使用FPGA加速,也会取得很好的效果。

VCK5000对于大多数开发者来说仍然是非常新的一款器件,由于VCK5000目前主要应用在数据中心进行AI推断方面的运算加速,所以开发者们对其性能和部署方式非常好奇

Xilinx的原语OSERDESE2是一种专用的并-串转换器,每个OSERDESE2模块都包括一个专用串行化程序用于数据和3状态控制。数据和3状态序列化程序都可以工作在SDR和DDR模式。

Vitis HLS 在从Vivaido HLS的升级换代中,以axi_master接口为起点的设计正在变得更易上手,其中很重要的一点就是更多的MAXI端口设计参数可以让用户通过指令传达到。这些参数可以分为两类

负责制定广为采用的PCI Express® (PCIe®)标准的组织PCI-SIG®今天宣布正式推出PCIe 6.0规范,传输速度达到64GT/s,是PCIe 5.0规格数据速率的两倍