【干货分享】优化rootfs的大小

judy 在 周日, 09/27/2020 - 14:41 提交

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。

本次研讨会话题包括:车载RTOS系统、Hypervisor 虚拟化、分布式开发框架、赛灵思汽车级产品方案等。

9月25日,米尔官方发布,其MYD-CZU3EG开发板在原产品的基础上搭载了Xilinx深度学习处理单元DPU,该部分新功能的增加可以极大的提升产品数据处理与运行效率,为AI应用落地提供完整支撑,帮助用户实现更为快速的产品开发和迭代。

本文描述了一种使用专用高速收发器的多速率串行接口。该设计基于非整数数据恢复单元,将数据速率下限扩展到0 Mb/s。

近几年,新一代的雷达初创公司开始瞄准高分辨率突破,这种雷达不仅能感知道路上体积较小的障碍物,还能生成周围环境的点云图像,使其具备激光雷达传感器的性能,而且不牺牲恶劣天气的表现。

该网络研讨会介绍了赛灵思的实时转码视频服务器(Real-Time Video Server)参考架构,并演示如何部署更有效的视频流工作负载,从而帮助流媒体服务供应商开发专用设备以优化流媒体网络,同时实现最低成本,最高通道密度和最低功耗。

PowerAI Vision 使具有深度学习的计算机视觉更易为企业用户所用。现在,您可在 Xilinx® Alveo™ FPGA 上部署 POwerAI Vision 模型,并了解如何将 Vitis™ 库集成至面向 Vision AI 任务的整个工作流程中。

赛灵思和大陆集团今日宣布将通过 Zynq® UltraScale+™ MPSoC 平台支持大陆集团开发新款高级雷达传感器 (ARS) 540,联手打造汽车行业首款量产版 4D 成像传感器

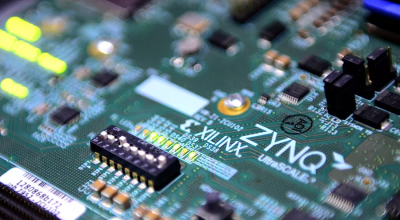

ZYNQ架构:双核ARM Cortex-A9 处理器:ARM Cortex-A9 是一个应用级的处理器,能运行完整的像Linux 这样的操作系统,传统的现场可编程门阵列(Field Programmable Gate Array,FPGA)逻辑部件:基于Xilinx 7 系列的FPGA 架构

Messaging Classification Appliance(消息分类工具)由 Xilinx 和 Supermicro 合作推出,是一种预封装的软件和硬件解决方案,可通过理解语义内容(消息的含义和意图)实时大规模地过滤、分类和路由消息流。