牛!Spartan 系列器件销量破 10 亿!

judy 在 周三, 10/21/2020 - 09:18 提交

近日,赛灵思公司再度取得一项里程碑式成就——Spartan 系列器件销量突破 10 亿!这是赛灵思其他产品组合都尚未企及的重要里程碑。作为赛灵思成本优化型产品系列中的旗舰款,Spartan 系列器件始终备受业界青睐,每一代产品都能为工业、消费和汽车应用带来全新的前沿功能,包括任意连接、传感器融合以及嵌入式视觉。

近日,赛灵思公司再度取得一项里程碑式成就——Spartan 系列器件销量突破 10 亿!这是赛灵思其他产品组合都尚未企及的重要里程碑。作为赛灵思成本优化型产品系列中的旗舰款,Spartan 系列器件始终备受业界青睐,每一代产品都能为工业、消费和汽车应用带来全新的前沿功能,包括任意连接、传感器融合以及嵌入式视觉。

XAPP1305 提供一个带 PCS/PMA 内核的 SGMII 示例,称之为“PS EMIO SGMII”。它不使用 FPGA 外部的 PHY 设备。对于我的使用案例,我想使用具有 SGMII 接口的外部 PHY 来连接。Linux 只能通过在设备树中设置 phy-handle 的 MDIO 管理一个 PHY。这个系统中有两个 PHY。怎么管理这两个 PHY?

本指南描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。

本方案基于Vitis-AI、ZCU104验证平台和AWS-IoT GreenGrass,其中Vitis-AI用于COVID-19深度学习模型的转换、量化和编译,将模型转换为DPU可运行的.elf文件;ZCU104验证平台完成基于X-Ray图像的COVID-19 CNN在线检测或用作AWS-IoT GreenGrass的边缘计算设备,完成COVID-19的边缘实时检测。

FPGA (Field Programmable Gate Aray,现场可编程门阵列)是一种可通过重新编程来实现用户所需逻辑电路的半导体器件。为了便于大家理解FPGA的设计和结构,我们先来简要介绍一些逻辑电路的基础知识。

有时我们需要在设计网表的基础上微调一下逻辑,这样可以无需修改代码,也无需重新做综合,在设计调试中可以节省时间同时维持其他逻辑无任何改动。这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

ZYNQ UltraScale+ MPSoC支持支持USB3.0,其功能通过PS侧GTR接口实现。实际设计中,有时希望仅支持USB2.0即可。这里,概要描述仅需要USB2.0场景下的软硬件设计及调试过程。我们在实际设计中,采用了与ZCU102相同的USB PHY芯片(Microchip/USB3320)

Zynq UltraScale+ 的隔离设计流程主要介绍如何使用支持 Xilinx Vivado 设计套件的 Xilinx IDF 实现安全关键型设计。

通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。按照AXI互联机制我们知道,我们的自定义IP是通过AXI_Interconnect连接到Master端,整体的框图也比较简单,为了验证方便我们只按照红色线路径进行测试。

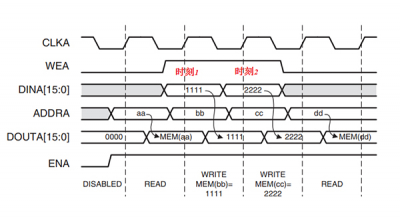

当我们调用RAMO的IP时,无论是单端口还是双端口模式,都会有个选项,可能很多人都没注意过这个选项,记得毕业季去华为面试的时候,还问过我这个问题,当时也是没答上来。后来也发现很多面试官都喜欢问这个问题,今天我们就来讲一下。