暑期学校优秀项目分享|手写体数学公式计算器

judy 在 周一, 08/10/2020 - 11:20 提交

本项目主要设计了一个手写体数学公式的计算器,其主要功能包括:首先从USB摄像头或者SD卡上存储的图片数据获取图像的输入,随后在Arm核上将其转变为单通道灰度图像,然后根据像素阈值确定图像内可能存在数字或者数学符号的区域,并将该区域的像素点提取出来

本项目主要设计了一个手写体数学公式的计算器,其主要功能包括:首先从USB摄像头或者SD卡上存储的图片数据获取图像的输入,随后在Arm核上将其转变为单通道灰度图像,然后根据像素阈值确定图像内可能存在数字或者数学符号的区域,并将该区域的像素点提取出来

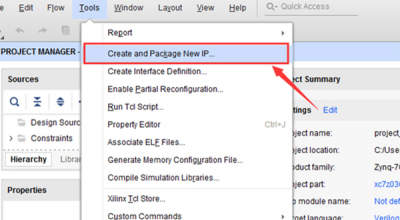

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多

相比于训练后量化方法,将量化过程插入到训练中可以弥补量化产生的误差,但是带来的问题可能是增加了训练的时间。在tansformer的量化实现中,我们采用了训练中量化的方法,在网络前向传输中,对权重等参数进行线性量化。

通过本次网络研讨会,了解如何使用 Vitis AI 部署和运行您针对 Xilinx 嵌入式 SoC 和 Alveo 加速平台预先训练好的 DNN 模型。然后开始使用 Vitis AI 在板上运行示例。

本文描述如何从 Vivado® 高层次综合移植到 Vitis™ 高层次综合。

本篇博文主要讲解了动态更改 UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法。

本次由信息技术新工科联盟主办,Xilinx、东南大学,西南交大联合承办的暑期学校已经在8月3日落下帷幕。从7月20日到8月3日这十五天间,超过1200名学员在全世界各地通过互联网参与了这一次暑期学校,累计了100小时的实践,超过10位讲师的精彩分享。

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过M_AXI接口对数据进行读取操作,此时设计一个基于AXI-Slave接口的IP进行数据传输操作就非常的方便

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

Vitis AI1.1 系列教程