Xilinx 自适应芯片助力部署灵活、可扩展的 5G 网络

judy 在 周四, 07/23/2020 - 09:20 提交

自从工信部 2019 年 6 月初发放 5G 牌照以来,中国 5G 建设一直在不断加速,预计 5G 基站数量将在 2020 年超过 50 万个。由于 5G 技术目前仍处在快速更新状态,因此基站必须具备足够的灵活性以应对技术的持续优化,这就为可编程芯片提供了广阔的舞台。作为全球首屈一指的 FPGA(现场可编程门阵列)供应商,赛灵思也迎来了全新的发展机遇

自从工信部 2019 年 6 月初发放 5G 牌照以来,中国 5G 建设一直在不断加速,预计 5G 基站数量将在 2020 年超过 50 万个。由于 5G 技术目前仍处在快速更新状态,因此基站必须具备足够的灵活性以应对技术的持续优化,这就为可编程芯片提供了广阔的舞台。作为全球首屈一指的 FPGA(现场可编程门阵列)供应商,赛灵思也迎来了全新的发展机遇

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。

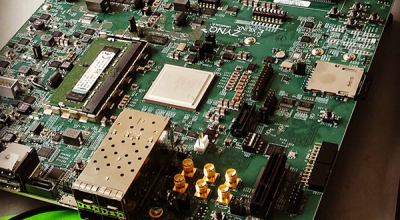

赛灵思 Kintex® UltraScale+™ FPGA 支持 -3、-2 和 -1 速度等级,其中 -3E 器件性能最高。-2LE 器件和 -1LI 器件可以 0.85V 或 0.72V 的VCCINT 电压工作,并提供更低的最大静态功耗。

得益于人工智能的发展,它在机器人、物联网和智能个人助理(如Siri和Alexa)等方面创造了惊人的发展。那什么是人工智能呢?人工智能最简单的定义是:收集有关世界的数据,并利用这些数据进行短期和长期的预测。

fifo是FPGA中使用最为频繁的IP核之一,可以通过软件自动生成,也可以自主编写。下面介绍vivado的fifo生成步骤

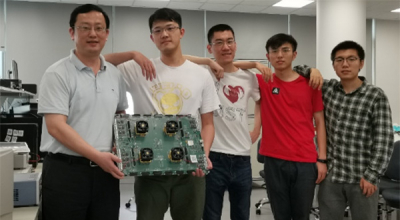

2020年7月21日,由集成电路自动化设计顶级会议DAC主办的第三届【低功耗目标探测系统设计挑战赛】落下帷幕,本届比赛旨在为终端设备设计高精度且高能效的物体检测系统,共吸引了来自全球多个知名研究机构共80支队伍参加,竞争非常激烈。来自北京工业大学的BJUT_Runner团队和上海科技大学的SkrSkr团队包揽冠亚军

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多。但我们大多数的工程还是无法避免使用HDL来连接两个module

本章将着重讲述TLP的数据链路层组成与操作,上一篇更新应该为第五讲,数据链路层位于事务层和物理层之间,使用容错和重传机制保证了数据传输的完整性和一致性,此外,数据链路层还需要对PCIe链路层进行监控和管理。

在某些情况下,比如远程工作时,可能需要访问本地不可得的器件。本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归同事所有的开发板。