详解Xilinx JESD204B PHY层端口信号含义及动态切换线速率

judy 在 周一, 11/04/2024 - 17:28 提交

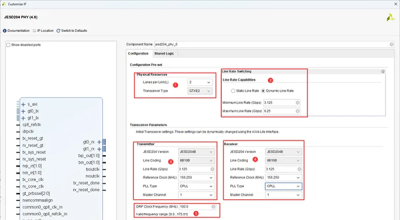

Xilinx官方提供了两个用于开发JESD204B的IP,其中一个完成PHY层设计,另一个完成传输层的逻辑,两个IP必须一起使用才能正常工作

Xilinx官方提供了两个用于开发JESD204B的IP,其中一个完成PHY层设计,另一个完成传输层的逻辑,两个IP必须一起使用才能正常工作

今天我们以一个端到端的例子来演示在Petalinux使用过程中,如何给u-boot的源码生成patch并在Petalinux中编译。

在mig使用的过程中,总会遇到各种各样的问题。总结起来也就是几种常见的问题,在上板测试的过程中注意到这些细节,一般都可以达到事半功倍的效果

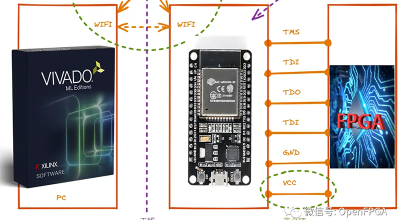

远程调试在整机调试时是很有必要和方便的,今天带给大家一个通过无线wifi下载调试fpga的一种方法

中科亿海微期待以联合实验室为切入点,双方能够基于行业发展趋势和人才培养目标,共赴未来,赋能核心技术研发,推动产品创新突破,集智攻关,共创辉煌。

本文配置JESD204B PHY的参数,分析其示例工程,并且对该IP进行仿真,由于该IP只是物理层,并没有上层协议,因此与GTX/H其实没有太大区别。

Basler视觉方案利用 FPGA处理流程简化了这一过程,通过直接在FPGA上运行Blob分析,提高了方案的实时性能

本文将为你揭开寻找FPGA IP核和HDL模块资源的神秘面纱。

长期以来,人们对用FPGA实现的创新大张旗鼓,对里面使用的FPGA保持秘而不宣。

用于构建 AMD embeddedsw 组件的旧方法将 .xsa 用作来自硬件人员的交接文件,并将 mdd、mld 和 mss 文件用于不同的软件配置