文章来源:FPGA的现今未

在mig使用的过程中,总会遇到各种各样的问题。总结起来也就是几种常见的问题,在上板测试的过程中注意到这些细节,一般都可以达到事半功倍的效果。

initial done

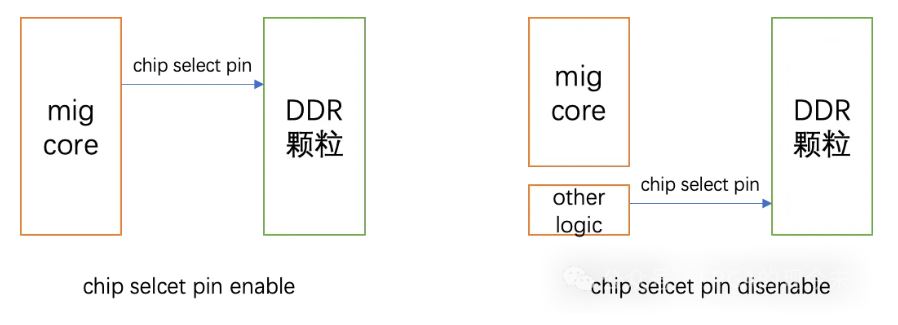

这个时候需要其他的逻辑重新产生chip select pin信号,输出给ddr3颗粒,使得颗粒能正常工作。

(2)硬件走线信号不好导致DDR无法initial done。项目计划将ddr 的IO时钟提升到800MHz,以满足将来设计的需求。但是,800MHz的版本在上板测试时出现initial done无法拉高的情况。首先开始怀疑的是mig core的生成问题,因为800MHz版本是第一次测试,后来更换400MHz的版本做对比测试,发现400MHz的版本正常,对比mig core的生成参数,主要就是IO时钟的不同。然后更换老的板子再做对比测试,800MHz的版本initial done信号也能拉高,因此基本确定是硬件问题。

(3)时钟复位信号错误引起initial done信号无法拉高。这些问题相对比较简单,时钟问题就是mig core在例化时选择的时钟(参考时钟、系统时钟等),和实际给的时钟是否一致。另外一个就是复位的极性,例化时选择的极性和实际给你的复位要保持一致。

数据错误

在测试过程中出现的另一种问题就是数据错误,这类问题的原因,一般就是2种情况,第一种情况就是mig core 用户侧的时序处理不对,导致正常的数据没有写入ddr中,这类问题比较好定位,通过一些检测手段就可以定位;第二种情况就是用户侧逻辑在处理读写操作过程中出现错误;

(1)写地址覆盖问题,某个地址被写入以后,还没有把数据读出来,又被新的数据覆盖一次,导致第一次写入的数据丢失。通过测试发现,只有某一个地址读出的数据有错误,重新加载或者复位后再测试,出现的错误一样,还是该地址读出的数据有错。 后面通过测试、分析,定位到原因:测试激励程序不够严谨,在随机的过程中出现了相同的地址,导致被覆盖,虽然这个问题是因为测试激励的问题,但是对于实际用户侧逻辑来说,同样具有参考意义,也可以通过对写地址产生逻辑的检测来确定问题根因。

(2)读出的数据混乱,这类问题其实相对好定位,读数据错误的问题往往是内部fifo缓存数据时处理不当导致的。前期在使用测试程序读写DDR的时候,只测试到长度最大为2K的数据,在实际应用过程中,读写的数据长度为4K,导致数据从DDR中读出后再缓存的过程中FIFO溢出。这类问题好定位是因为可以通过对FIFO状态的监控来确定问题所在点。

总结

在使用mig的过程中出现的错误,大部分的场景下,还是有优先排查自己的设计和代码,另外充分利用好example design也是一个不错的选择。