Vivado管脚定义方法

joycha 在 周三, 06/03/2020 - 08:25 提交

赛灵思的文档繁多,本来可以用简单的方法能够实现,却没有简明的文档进行说明,给新进者带来困扰,下面我来介绍下用Vivado工具定义管脚的两种方法。

赛灵思的文档繁多,本来可以用简单的方法能够实现,却没有简明的文档进行说明,给新进者带来困扰,下面我来介绍下用Vivado工具定义管脚的两种方法。

Linux下,可以在设备树里保留一段内存,留给用户自己管理和使用,Linux保证不会使用保留内存。在使用中,有人发现,保留内存不能使用非对齐的方式访问。经研究,如果在保留内存时,声明了“no-map”属性,Linux会把这段内存映射为strongly order模式,不支持非对齐的方式访问。

GTX是kintex-7系列FPGA内部的高速数据收发器硬核模块,专门用于FPGA与外部的高速数据通信,目前许多常用的高速协议(比如JESD204、PCIE、SATA、SGMII接口的以太网等)的实现都需要用到GTX。GTX的基本内容以前介绍过了,这里不再叙述。该篇主要记录两片FPGA利用各自的GTX实现高速数据的收发过程

Xilinx 公司的芯片有一整套命名规则,可以通过相关文档查阅。

区块链具有广泛的互联网应用。它可通过设计来分散,因此是许多传统事务处理系统的替代方案。为了使区块链系统可行(可扩展性、可互操作性和可持续性),与区块链相关的复杂耗时/耗电的加密工作应该转移到加速系统中。我们的解决方案是一款安全的公共密钥基础架构引擎,可用来卸载计算密集型公共密钥工作,比如签名生成与验证

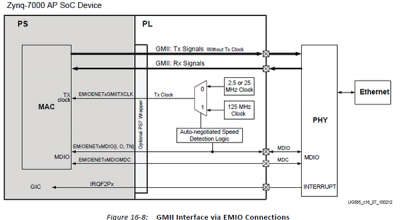

本例程将 PS 的 ETH1 通过 EMIO 方式引出, 通过 EMIO 引出的 ETH 为 GMII 接口, 将其与 GMII to RGMII IP 核连接后转换成 RGMII 接口,然后与外部子卡中的 88E1512 芯片连接。在 PS 端通过 SDK 自带的 lwip echo server 例程通过子卡,以 RJ45 电口与 PC 机实现 TCP 网络通信

Xilinx的28nm、16nm SoC在业界应用非常广泛。最近也发布了7nm的SoC器件Versal VC1902和对应的开发板VCK190。Versal是新一代的异构计算平台,包含A72、R5、及内部管理用的CPU。Versal的软件开发工具是Vitis。

时延敏感网络(TSN, Time Sensitive Network)是指能保证时延敏感流的服务质量,实现低时延、低抖动和零丢包率的网络。时延敏感流可分为周期时延敏感流(PTS, Periodic Time Sensitive),比如工厂里的循环控制指令、同步信息,和非周期/零星时延敏感流(STS,Sporadic Time Sensitive),比如事件告警信息。

这一期我们将给大家带来的是第三届全国大学生FPGA创新设计竞赛特等奖作品——基于PYNQ的散射成像相机CC Cam。该作品由来自东南大学的陈欣玥,雷弈,刘可同学设计完成。她们的作品同样基于Xilinx的PYNQ开源软件框架,同时也使用Xilinx的高级综合工具HLS设计了加速算法IP核。

本文介绍如何利用赛灵思 Alveo 卡实现应用加速的简介,包括阐述基本架构方法、识别适用于加速的代码以及利用软件 API 以最有效的方式来管理存储器并充分发挥 Alveo 卡的强大作用。