是时候“KO”时延问题了!

judy 在 周三, 05/20/2020 - 16:20 提交

在证券交易领域,行情数据瞬息万变、盈利机会转瞬即逝,因此“低时延”是金融交易追求的核心目标。这也正是Enyx公司备受金融行业青睐的原因:2019年,著名交易技术提供商Vela宣布Enyx为美国股票提供下一代基于FPGA的股票行情自动收录器设备,该设备将延时减少一半以上。

在证券交易领域,行情数据瞬息万变、盈利机会转瞬即逝,因此“低时延”是金融交易追求的核心目标。这也正是Enyx公司备受金融行业青睐的原因:2019年,著名交易技术提供商Vela宣布Enyx为美国股票提供下一代基于FPGA的股票行情自动收录器设备,该设备将延时减少一半以上。

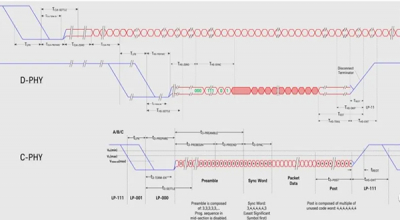

MIPI是移动领域最主流的视频传输接口规范,没有之一,目前应用最广泛的是MIPIDPHY和MIPI CPHY两组协议簇,其中CSI-2主要用于图像接入,DSI-2主要用于图像输出。本文主要以CSI-2为例进行仔细说明,DSI-2雷同,举一反三即可。

本文介绍了Wireshark的快速FPGA实现FFShark。其结果是一个紧凑的、相对便宜的直通设备,可以插入任何正在运行的100G网络中。数据包将在FFShark中传输,不会中断,并且附加的延迟最小

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。Vivado 提供了预编译的 UVM V1.2 库。请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。本文随附了 1 个简单示例,可供您下载解压使用。

调制就是把要传递的信号“搬运”到规定的频率附近,从技术上说,天线的尺寸和电磁波的波长差不多的时候,才能获得较高的发射效率,假设信号是10MHz,那么波长为30m,这么长的天线显然是不现实的。因此需要把信号调制到较高的频率,减少天线的尺寸

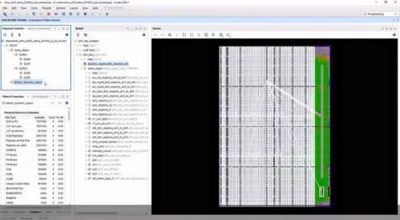

本视频解读 DFX 布局规划基本信息视频,介绍了扩展布线区域的使用。这项 Vivado 功能面向 UltraScale 和 Ultrascale+ 器件,可改善 DFX 设计结果,设计人员创建其布局规划时应考量如何运用此功能

本周,IBM声称,其神经计算机系统达到了每秒120万帧的训练时间,创下了最新记录。IBM在AI模型训练上实现了大突破,可与最先进的技术相匹敌。网友对此表示简直不敢相信!

上期我们分享了王伟老师的 技术文章解析(上),本期将会给大家带来下集解析,Ultra96v2petalinux 2019.2软件平台设计与调试和Vitis AI Linux加速平台的介绍。

作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

本视频围绕 UltraScale 和 UltraScale+ 架构,回顾了 DFX 布局规划基本信息;并提供了通过创建更优化的布局规划来改善设计结果的策略和技巧。