【视频】Vitis 命令行流程中的 GDB 调试

judy 在 周二, 04/07/2020 - 16:21 提交

该视频介绍了如何在 Vitis 命令行流程中进行 GDB 调试。视频前半部分简要介绍了流程。简介之后有一个有关在 Vitis 中进行 GDB 调试的演示。

该视频介绍了如何在 Vitis 命令行流程中进行 GDB 调试。视频前半部分简要介绍了流程。简介之后有一个有关在 Vitis 中进行 GDB 调试的演示。

本篇主要参考其官方文档介绍JESD204IP核的端口信号含义,其实该篇本人写起来挺无聊的,大家读起来应该也很枯燥,但开发JESD204时每个端口信号的含义和使用规则必须了然于胸,所以不得不仔细解释一些端口信号,以后忘记了就当中文手册查看吧~

SP701 是一款基于赛灵思 Spartan®-7 FPGA的评估套件,Spartan-7 FPGA 是赛灵思 28nm 7系列 FPGA 中最佳性能功耗比的器件系列,是传感器密集型应用(如工业网络、嵌入式视觉和汽车等)的理想选择。本文作者赛灵思工业业务部市场营销主管 Michael Zapke ,就如何在工业领域发掘该开发板的价值提供了详细攻略

基于FPGA的灵活可配置以及强大扩展能力,PYNQ板卡可以连接各种外设,比如Seeed Studio和DFRobot就有大量的传感器外设可供选择,结合AWS Greengrass等IoT解决方案 (国内BAT公司也有类似解决方案), 就可被应用于工业物联网、智能家居等应用场景,也可以使用到无人驾驶等领域。

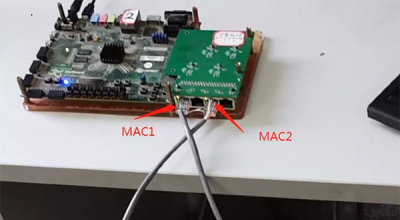

同学们在学网络课程的时候都知道,除巨帧外,常见的以太网帧的长度范围是64字节到1518字节,并且因为最初总线型半双工的组网原因,人们制定了CSMA/CD协议,规定了以太网中最短帧为64字节。然而,互联网的发展日新月异,今天的网络早已不是当初的半双工模式

在这篇新博文中,我们来聊一聊如何将 AXI VIP 添加到 Vivado 工程中,并对 AXI4-Lite 接口进行仿真。随后,我们将在仿真波形窗口中讲解用于AXI4-Lite 传输事务的信号。

IBM PowerAI Vision 可简化 AI 模型的构建与部署过程,无需 AI 专业技术,便可实现图像分类和对象检测等功能。 现在,您可使用 IBM PowerAI Vision 通过 Xilinx Alveo U50 灵活应变的加速卡来加速推断。 IBM PowerAI Vision 使用 Xilinx Vitis AI 与 FPGA 集成,因此不必成为 FPGA 开发人员,便可利用其优势

首先要下载Ultra96的开发板定义文件(Board Definition Files),https://github.com/Avnet/bdf,从GitHub上下载AVNET所有开发板文件,如下所示

近日,据冰岛国家广播公司网站报道,当地一名新冠肺炎患者被检测出体内存在两种新冠病毒,可能是全球首个“双重感染者”。中国科学院院士周琪 26 日接受采访时也曾指出,病毒要存活下来变异是必然的。面对正发生快速变异的新冠病毒,监视并及时有效地发现潜在的病毒变异成为全球抗疫新阶段的重点

疫情期间是真爽,睡觉睡得我啥也不想干,本来也琢磨着继续更新,无奈开工就很忙,天天只想睡觉,自从爽了一个月,我就只想睡觉,看来我要买点亚麻籽油提提神了,碰巧最近有网友问他的双核没法正常工作,我试了下,是可以的,但是这当中也遇到点bug,好吧,开始干活吧