无线通信中的扰码

judy 在 周一, 03/09/2020 - 09:41 提交

对数字信号的比特进行随机处理,减少连0和连1的出现,从而减少码间干扰和抖动,方便接收端的时钟提取;同时又扩展了基带信号频谱,起到加密的效果。为了保证在任何情况下进入传输信道的数据码流中“0”与“1”的概率都能基本相等,传输系统会用一个伪随机序列对输入的传送码流进行扰乱处理,将二进制数字信息做“随机化”处理

对数字信号的比特进行随机处理,减少连0和连1的出现,从而减少码间干扰和抖动,方便接收端的时钟提取;同时又扩展了基带信号频谱,起到加密的效果。为了保证在任何情况下进入传输信道的数据码流中“0”与“1”的概率都能基本相等,传输系统会用一个伪随机序列对输入的传送码流进行扰乱处理,将二进制数字信息做“随机化”处理

Pblock是对一些逻辑实行物理上的约束,即把一些逻辑绑定到FPGA上固定的资源区域内。它是优化走线,改善时序的一种很重要方法。Pblock的大小限定了该逻辑单元使用的FPGA资源,pblock的位置限定了逻辑单元在FPGA中的位置。通常一个pblock大小不要超过总设计资源的20%。如果pblock占比资源很大,就要将一个pblock划分给更底层的逻辑

本文深维科技联合创始人兼CEO樊平详细剖析了图片加速的必要性、当前实际的图片解决方案与部署方式以及如何通过FPGA+CPU异构计算的方案维护用户体验与服务成本新平衡。

我很有幸从第一届亚太地区设计自动化会议(ASP-DAC)起就参与到ASP-DAC这个大家庭。我的第一篇ASP-DAC论文是1995年在日本千叶的首届会议发表的”Exploiting Signal Flow and Logic Dependency in Standard Cell Placement”[3]。这篇文章讨论了如何利用逻辑综合的信息来提高标准单元布局的结果

图像信号处理器 (ISP) 是照相机和摄影机内部的数据处理模块,可将摄影机图像传感器的原始输出转换为我们熟悉的图片和视频。虽然 ISP 最初是使用数字信号处理器 (DSP) 实现的,但当前需要的高性能视频标准为该功能定制了硬件模块

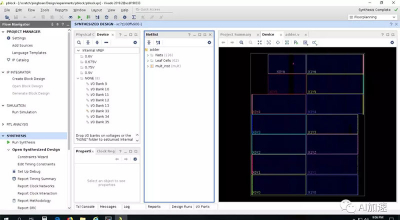

最近在看Xilinx新出的工具Vitis,这个工具咋说呢,改了好多。。

之前的SDSoC,SDAccel统一被Vitis来实现

之前按的SDK直接被Vitis替代

今天,赛灵思宣布推出业界首款 “一体化 SmartNIC 平台”— Alveo™ U25,在业界首次真正在单卡上实现了网络、存储和计算加速功能的完美融合。U25 专门针对当前那些在不断增长的联网需求和不断上涨的成本之中苦苦挣扎的云服务提供商、电信公司和私有云数据中心运营商而设计

GigaIO 的 FabreX 是采用纯 PCIe 技术的新一代网络架构。在 SC19 上,GigaIO 演示了几项应用,其可通过服务器、内存、IO 和加速卡(FPGA、GPU 等)的可组合性,实现性能、可扩展性、效率及更高资源共享利用率的卓越水平

Alveo™ U25 所提供的是一款一体化 SmartNIC 平台,真正在单个平台上实现了网络、存储和计算加速功能的融合。Alveo U25 SmartNIC 平台依托于功能强大的 FPGA,能够以最大效率实现在线硬件加速与卸载,同时可以避免不必要的数据传输与 CPU 处理

每年二月,阿姆斯特丹都会举办世界上规模最大的音视频与系统集成展会 - 欧洲集成系统展(ISE)。在这里,全球音视频行业齐聚一堂,共同分享业界领先的音视频项目以及尖端技术、产品与解决方案。AI/ML 相关的话题依然是各个行业的焦点所在,人工智能领域日益扮演领导角色的赛灵思,在 ISE2020 上有什么亮点和表现呢?