Python进阶:自定义对象实现切片功能

demi 在 周一, 10/14/2019 - 14:53 提交

切片是 Python 中最迷人最强大最 Amazing 的语言特性(几乎没有之一)。那么,我们是否可以定义自己的序列类型并让它支持切片语法呢?更进一步,我们是否可以自定义其它对象(如字典)并让它支持切片呢?

切片是 Python 中最迷人最强大最 Amazing 的语言特性(几乎没有之一)。那么,我们是否可以定义自己的序列类型并让它支持切片语法呢?更进一步,我们是否可以自定义其它对象(如字典)并让它支持切片呢?

上一篇咱们说了slice,提到了其与全局时钟在一起就可以实现任意的组合逻辑和时序逻辑功能,但很多时候咱们还需要将FPGA内部的数据暂时存储,用作它用。Slice作为FPGA最基本的单元,也是能够完成数据存储的功能,但显然有些大材小用,因此xilinx公司在其FPGA内部专门集成了很多存储器模块,称作Block RAM......

赛灵思可编程器件含有数百万个逻辑单元 (LC),集成了当前越来越多的复杂电子系统。本高层次生产力设计方法提供了在短设计周期内开发此类复杂系统的一套最佳做法。

Xilinx的官方文档在介绍FPGA的逻辑资源时通常是按照CLB(Configurable Logic Block)来介绍,把CLB作为FPGA里的最小逻辑单元。但是CLB是由2个slice构成,因此平时大家都把slice挂嘴边,称为最小的逻辑单元,很少提起CLB。因此本篇咱们就简要聊一聊slice的功能。对于大部分应用,咱们不必深入了解slice,写好代码后FPGA的开发软件会自动帮助咱们布局布线,所以本篇以了解为主,当然如果您是高级用户,是大佬级FPGA专家,就另当别论。

7系列FPGA的slice包含4个部分:

(1)逻辑功能产生器,也就是咱们常说的查找表,1个slice里包含4个6输入的查找表。

(2)存储单元,也就是常说的触发器,1个slice里包含8个触发器。每4个触发器为一组,可配置成D触发器或锁存器。

(3)多路复用器,也就是1位宽的数据选择器,数量非常多,足够使用。

(4)进位逻辑,它与本列的上下slice的进位逻辑相连,实现数据运算时的进位操作。

赛灵思开发者大会,一个前所未有的开发者与专家思想与观点,创意与方案亲密接触的平台。

参加 XDF,解锁 FPGA、可编程 SoC、ACAP 无限潜能,突破算力极限,加速应用部署,激发你的灵感,增强你的技能,让你的创新永不落伍!

全球 1,300 多名与会者、120 位演讲嘉宾、84 小时实验室项目和 40 多个合作伙伴演示。

Xilinx 及其联盟成员提供嵌入式工具与运行时环境可帮助您高效快速地将概念转化为生产。我们可为您提供使用 Xilinx Zynq® SoC 和 Zync UltraScale+ MPSoC 器件、MicroBlaze™ 处理器内核和 Arm Cortex-M1/M3 微控制器创建嵌入式系统所需的所有组件,包括开源操作系统和裸机驱动程序、多运行时和......

众所周知,我们可以通过索引值(或称下标)来查找序列类型(如字符串、列表、元组…)中的单个元素,那么,如果要获取一个索引区间的元素该怎么办呢?

Vitis™ 统一软件平台包括一组广泛的、性能优化的开源库,这些库提供了即开即用的加速功能,并且对现有应用实现最小化代码更改或零更改。

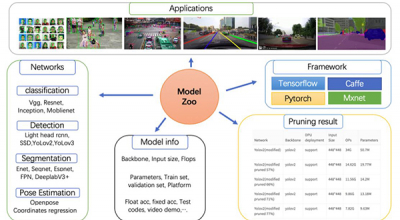

Vitis™ AI 是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

网上关于vivado开发zynq的资料很多,总结以下操作流程,以SD模式为例。