质的飞跃,英国 V-nova 描绘 Codec 世界新蓝图

demi 在 周四, 09/19/2019 - 10:14 提交

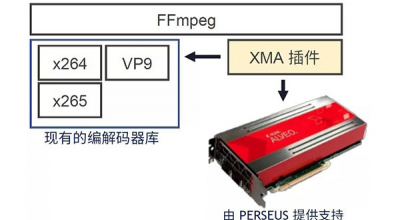

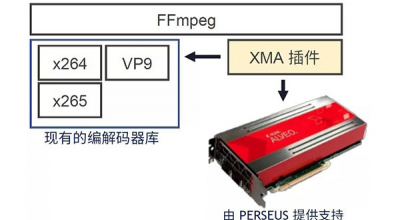

众多大规模视频服务运营商还在提供传统的 H.264 视频流,并通过通用 CPU 中进行编码。但是现在可以利用专用处理功能为视频编码效率带来质的提升,这些功能更适合像转码密集型应用。赛灵思 FPGA 上运行的 PERSEUS Plus 完全涵盖这些处理功能,可提供业界领先的压缩效率,从而显著改善大规模服务的编码密度,大幅度降低运营成本,并且提高体验质量 (QoE)。

众多大规模视频服务运营商还在提供传统的 H.264 视频流,并通过通用 CPU 中进行编码。但是现在可以利用专用处理功能为视频编码效率带来质的提升,这些功能更适合像转码密集型应用。赛灵思 FPGA 上运行的 PERSEUS Plus 完全涵盖这些处理功能,可提供业界领先的压缩效率,从而显著改善大规模服务的编码密度,大幅度降低运营成本,并且提高体验质量 (QoE)。

赛灵思开发者大会 ( Xilinx Developer Forum, XDF ) 2019 即将拉开帷幕!北京站报名通道现已开通!!

SDAccel™ 环境使用标准编程语言,提供开发和交付 FPGA 加速数据中心应用的框架。SDAccel 环境包括基于 Eclipse的综合开发环境 (IDE) 的熟悉的软件开发流程和能充分使用 FPGA 资源的架构最优化编译器。

时序不满足约束,会导致以下问题:编译时间长的令人绝望;运行结果靠运气——时对时错。

AXI_STREAM的时序:AXI_STREAM接口一般用于大规模持续的无地址映射关系的流数据传输......

连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述。连续赋值语句必须以关键词assign开始。

RapidIO是由Motorola和Mercury等公司率先倡导的一种高性能、 低引脚数、 基于数据包交换的互连体系结构,是为满足和未来高性能嵌入式系统需求而设计的一种开放式互连技术标准。RapidIO主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板(Backplane)连接。

一次常规调试中发现上电后交换机多个口同时打流会导致卡死的现象,最后一步步分析问题出现的原因是位宽不够导致的溢出。

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行;而双口有两组数据线与地址线,读写可同时进行;FIFO读写可同时进行,可以看作是双口;

在高速的同步电路设计中,时序决定了一切,要求所有时序路径都必须在约束限制的时钟周期内,这成为设计人员最大的难题,因此,首先确定和分析基本时序路径有助于设计者快速,准确地计算时序裕量,使系统稳定工作,XILINX公司提倡的几种常用基本路径。