分析以下内容:拆箱 RF 分析仪工具第一部分

demi 在 周四, 06/13/2019 - 12:05 提交

在上一篇博客中,我提到赛灵思已通过一个叫作 RF Analyzer 的工具在任何电路板上的任何器件上启用了 RF 数据转换器的调试功能。我现在将用接下来的两篇博文来拆箱此实用程序、查看其主要功能,并了解我们可以如何用它来管理 RF-ADC 和 RF-DAC 块。我还会讲讲如何用它来生成 RF-DAC 激励,以及如何查看和分析 RF-ADC 接收的数据。

在上一篇博客中,我提到赛灵思已通过一个叫作 RF Analyzer 的工具在任何电路板上的任何器件上启用了 RF 数据转换器的调试功能。我现在将用接下来的两篇博文来拆箱此实用程序、查看其主要功能,并了解我们可以如何用它来管理 RF-ADC 和 RF-DAC 块。我还会讲讲如何用它来生成 RF-DAC 激励,以及如何查看和分析 RF-ADC 接收的数据。

随着科学技术的快速发展,数据采集系统已广泛应用于航天、军事、工业、医疗等各个领域,尤其在高精度产品的检测和监控项目中发挥着至关重要的作用。在实际工程应用中,要求采集系统具有高速率、高精度、实时处理、系统稳定性好和通道数量多等特点。

在数字信号处理中,CIC滤波器是FIR滤波器中最优的一种,其使用了积分,梳状滤波器级联的方式。

CIC滤波器由一对或多对积分-梳状滤波器组成,在抽取CIC中,输入信号依次经过积分,降采样,以及与积分环节数目相同的梳状滤波器。在内插CIC中,输入信号依次经过梳状滤波器,升采样,以及与梳状数目相同的积分环节。

赛灵思视频 Video Processing Subsystem IP 核是为了便于使用而被封装到单个 IP 中的一组视频处理 IP。该核是基于 HLS 的 IP。这就是说当您将 IP 添加到设计中后,此核用 C/C++ 编写,然后在后台由 Vivado 转换为 RTL(VHDL/Verilog)。

本视频重点介绍了 V-Nova PERSEUS™,重新定义视频中的质量/码率权衡。

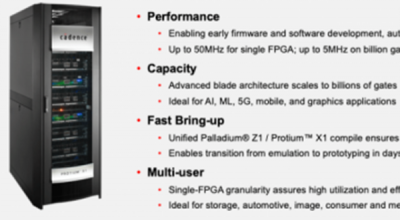

大型原型硬件对于投产前的现代固件和软件开发都至关重要,有数十亿门硬件。对于硬件验证,它补充了仿真,运行速度足够快,可以在大软件负载上进行实际测试,同时仍然允许快速切换到仿真,以便在需要的地方进行更详细的调试。

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。本文介绍时序分析的原理以及出现时序问题时一般的解决办法。

汽车是成像技术的关键市场!据麦姆斯咨询介绍,摄像头现已成为汽车的标配,2018年汽车图像传感器出货量为1.24亿颗。汽车摄像头模组市场在2018年达到30亿美元规模,预计2024年将达到57亿美元,2018~2024年的复合年增长率(CAGR)为11%。

在Xilinx官网找资料无意中在应用—>AI推断加速中看到了下面三张图,顿觉“众里寻他千百度,蓦然回首,那人却在灯火阑珊处”的意思了。三张图非常通俗易懂的介绍了FPGA/ACAP这样的体系结构在AI推理中的优势。

在计算机内存中,统一使用Unicode编码,当需要保存到硬盘或者需要传输的时候,就转换为UTF-8编码,这样可以节省很多存储空间。在python中,str和unicode都是basestring的子类,basestring有两个方法......