Xilinx verilog语法技巧——RAM的初始化

judy 在 周一, 05/20/2019 - 13:56 提交

RAM可以通过以下方式初始化:

1,在HDL源代码中指定RAM初始内容;

2,在外部数据文件中指定RAM初始内容。

RAM可以通过以下方式初始化:

1,在HDL源代码中指定RAM初始内容;

2,在外部数据文件中指定RAM初始内容。

什么时候我希望通过 Xilinx 分销商购买,而不直接通过 Xilinx 在线商店?

如何查找 Xilinx 授权分销商?

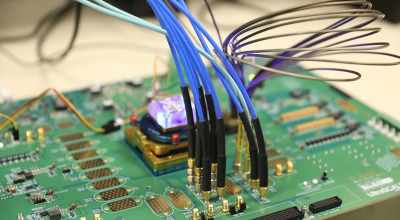

通过 Xilinx 58G 驱动 GTM 收发器和 Virtex® UltraScale+™ 集成强化 100G 以太网子系统,在两个通道上演示 100G 以太网。 该视频概述了 GTM 收发器如何使传统硬件支持 58G PAM4

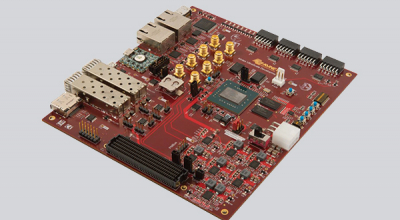

Xilinx 器件可通过精选芯片工艺和功耗架构为所有产品组合实现高电源效率,包括 Spartan-6 系列及 7 系列、UltraScale™ 以及 UltraScale+™ FPGA 和 SoC。对于每一代产品,Xilinx 都不断提升其节电功能,包括工艺改进、架构创新、电压缩放策略以及高级软件优化策略等。以下是特定产品组合功能的详细信息、芯片工艺优势和基准比较

在图像处理、计算机视觉领域,Lena数字图像被大多数的键盘侠广泛使用,Lena可以说是一张司空见惯的标准图。国外某期刊的主编,曾经说明过以下原因:1.Lena图像混合了各种细节、纹理特征、平滑区域和阴影部分,能够很好的测试图像处理的各种算法;2.Lena是个迷人的美女,做图像处理的研究者或工程师,大部分都是男的,不奇怪他们被Lena美女所吸引。

我们处在一个由数字计算机控制的模拟世界里。因此,物联网 (IoT) 设备的设计人员需要将模拟值高效地转换为采样数字表示。答案看似简单,使用一个前置的模数转换器 (ADC) 便能解决问题,然后 ADC 并非千篇一律。因此,设计人员需要了解各种拓扑,以及它们与应用的对应关系。

首先对于纯组合逻辑电路来说,其逻辑功能块的输出仅仅与当前的输入值有关系,其电路延时分析也非常的简单,只考虑输入到输出的信号延时Tdelay,但是影响Tdelay时间的因素比较多,比如不同的器件输入到输出的延时时间不同,不同的工艺条件以及在不同的环境下,Tdelay的时间也不同

最高层次的安全性和可靠性

Xilinx 可为客户提供综合而全面的 TUV SUD 认证设计流程解决方案,帮助他们在安全性和可靠性都非常关键的航空航天与国防、汽车、医疗和工业市场简化和加速基于功能安全规范的认证。

支持的功能性安全标准

VHDL 的一个强大功能是用库来组织 RTL 的不同部分。 通过使用库,不同的设计人员可以做这个工程中自己负责的那部分工作,而不必担心会在命名方面与其他设计师发生冲突。在例化期间,这可以通过手动指定要使用的库或者通过配置语句来完成。

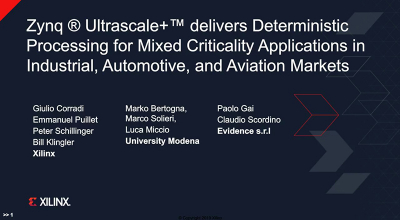

当前的市场需求正迫使我们在所有嵌入式应用中通过使用多核 SoC 增加计算需求,同时需要保存几十年前为单核处理器开发的原有实时代码。实时处理器的性能有限,设计人员通常需要考虑使用应用处理器来获得所需的性能,其代价是牺牲确定性和最坏情况执行时间 (WCET)。