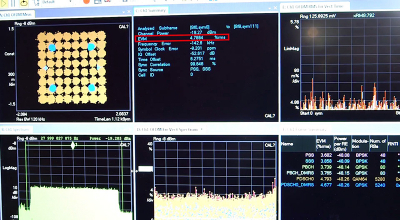

【视频】112G Long Reach PAM4

judy 在 周三, 03/27/2019 - 10:42 提交

112G PAM4 是业界通向更高带宽的下一步。该演示主要介绍 Xilinx 针对新一代系统提供 112G 的远景。

112G PAM4 是业界通向更高带宽的下一步。该演示主要介绍 Xilinx 针对新一代系统提供 112G 的远景。

各方竞争加剧,产品周期缩短,哪些底层技术将最快获益?2019年4月11日,赛灵思 AI 市场发展总监刘竞秀将出席第八届EEVIA年度中国ICT媒体论坛暨2019产业和技术展望研讨会,通过“赛灵思人工智能平台-人工智能边缘计算加速引擎”的主题演讲,分享人工智能时代,灵活应变的赛灵思平台如何与人工智能发展的速度完美匹配,如何从各种传统的计算方案中脱颖而出,成为行业发展的大势所趋

AI 硬件亚洲峰会(AI Hardware Asia Summit) 将要拉开帷幕。这是该系列全球活动的第二个专场,会议主题为 AI 加速器技术以及用于处理深度学习、神经网络和计算机视觉的芯片和系统设计与应用。赛灵思人工智能高级总监单羿将发表题为 “基于FPGA的AI平台、技术、应用和生态系统” 的主题演讲

Xilinx 工具与方法高级应用工程师谢 敏在赛灵思技术日上分享《Alveo 数据中心加速卡快速入门》

时钟信号是FPGA时序逻辑设计中必不可少的条件,一般情况下在FPGA始终资源充裕的情况下通常采用FPGA内部自带的内核生成时钟信号,例如DLL/MMC,但是一旦出现资源不够的情况,就只能另寻他法了

与 O-RAN 联盟成员 AT&T、Anokiwave、Ball Aerospace 和 Keysight 合作,实现了 O-RU 概念验证演示。

本课程向新老设计人员介绍了 UltraScale™ 器件架构的最新内容,包括介绍全新CLB资源、时钟管理资源(MMCM 和 PLL)、全局和区域时钟资源、存储和DSP资源、源同步资源及IO接口模块特性。 同时,也阐述了如何将原有设计移植到最新UltraScale器件架构上

Xilinx 大中华区业务拓展总监朱勇在Xilinx技术日上分享《无与伦比的并行处理—FPGA加速度基石》

Xilinx FPGA器件内部有专用的硬件资源,支持大量设计时钟的使用。通常板子上有一个外部组件(如有源晶振)产生时钟信号,通过输入端口进入器件内部。外部时钟可以通过MMCM、PLL、BUFR等特殊原语生成其它时钟,也可以由LUT、寄存器等常规单元进行转换(通常称作门控时钟)。本文将讲述如何根据应用情况定义时钟

FPGA设计的特点是需要不断不断的迭代各个设计流程来达到最终的设计,同时迭代的成本大,它比单片机开发更注重迭代的开发思想。所以,设计的前期一定要从系统的角度考虑好系统的方案,然后在系统这个方案中不断的迭代,不然后期发现由于系统方案的问题就得不偿失了,好的系统架构就是成功一大半了