FPGA实践教程(七)运用IPcore调用DDR

judy 在 周五, 03/15/2019 - 10:35 提交

目的:直接运用IPcore调用DDR

目的:直接运用IPcore调用DDR

如果说云计算以速度取胜,那么边缘计算则在速度的基础上更讲究灵活应变,从而百花齐放。边缘计算应用专场将会为您带来应用于各种领域中的赛灵思人工智能方案,与您共同探讨万物智能的实现方式

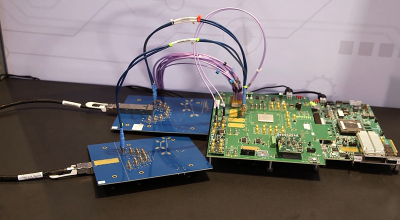

在 DesignCon 2019 上,Xilinx 和 Luxshare 展示了 112G PAM4,运行于超过 1 米的直接连接铜 OSFP 铜缆。 观看视频,了解这些公司如何合作实现高速连接的未来

所谓“天下武功,唯快不破”,云计算时代,得速度者得天下。云计算加速分会场将通过 Alveo 数据中心加速卡的现场演示与讲解,以及针对不同应用和领域的方案详解,带您快速跨入云计算加速的跑道。

为了满足老师们学习新技术的需求,依元素科技将于2019年3月23日在南京开展每月一次的FPGA师资周末集训营,本集训营完全免费,没有费用的压力,让您可以每期都参加直到您熟悉为止。

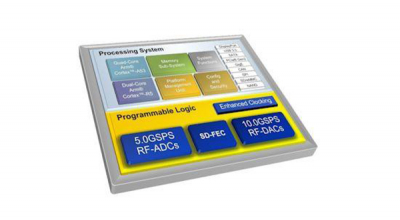

随着通信行业逐渐向5G标准靠拢,移动设备制造商十分钟情于技术试验和概念验证测试。现在,这些技术的商业可行性正在进行严格评估,然而原型设计所使用的很多技术都无法很好地转化为商业部署。为加速解决5G部署问题,不久前,Xilinx公布了其下一代Zynq Ultrascale+ RFSoC单芯片自适应无线电平台

在 DesignCon 2019 上,Xilinx 和 TE 展示了一对演示。首先,UltraScale + FPGA 中的 32G Xilinx GTY NRZ SERDES 通过 TE Sliver 连接器运行。 接下来,Virtex UltraScale + GTM PAM4 收发器通过 TE SFP-DD 连接器和直接连接铜缆发送数据

编译PetaLinux时,使能GDB。单板上就会有GDB。zcu106的VCU TRD 2018.2 已经包含GDB。带调试信息编译软件,比如添加-g, 或者-g3开关。对于zcu106的ctrl-sw,在encoder_defs.mk里修改CFLAGS, 添加-g3,得到CFLAGS+=-Wall -Wextra -g3

赛灵思技术日活动(Xilinx Technology Day)上海站即将拉开帷幕,六大重磅主题演讲人及嘉宾,将为与会者带来FPGA 行业趋势及赛灵思最新产品及技术动态最专业、最精准的分享。

2019年3月21日,赛灵思大中华区销售副总裁唐晓蕾将应邀出席2019 AI 芯片技术论坛,并发布题为“Xilinx 自适应平台 – 全方位创新的基石”的主题演讲。同时,她还将出席该会议当天的高端对话环节,就人工智能领域普遍关注的人工智能创新及赛灵思灵活应变的平台解决方案分享观点和见解