Zedboard学习(七):VGA显示

judy 在 周二, 01/29/2019 - 10:46 提交

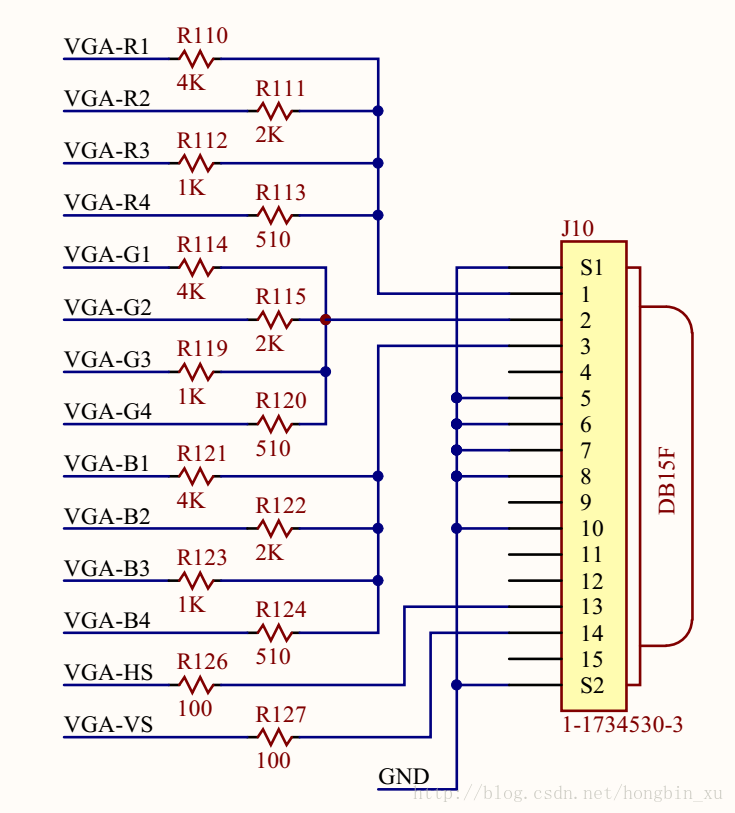

VGA硬件接口

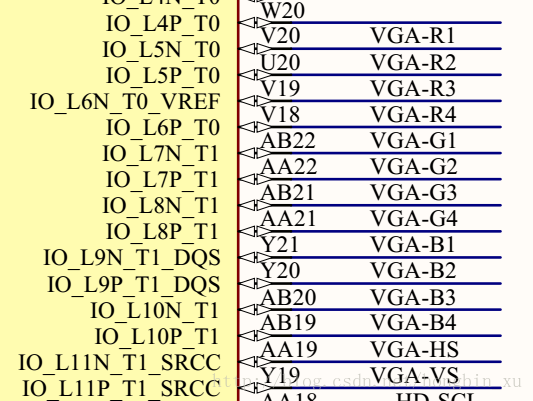

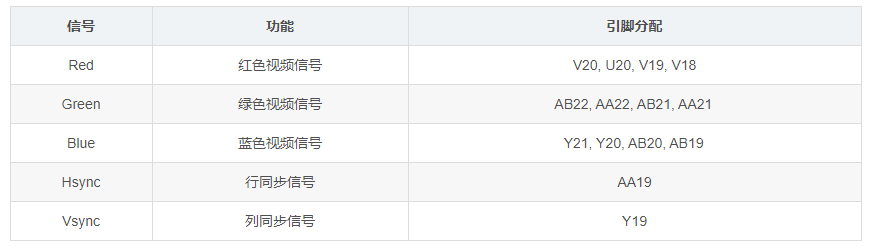

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

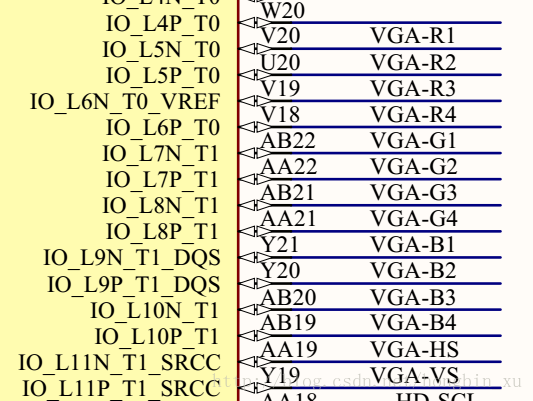

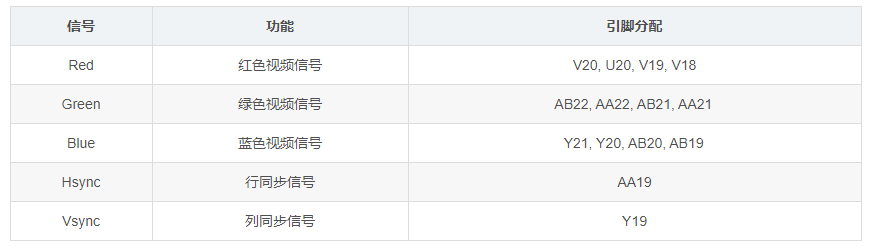

上面给出了所有的引脚分配。

VGA时序分析

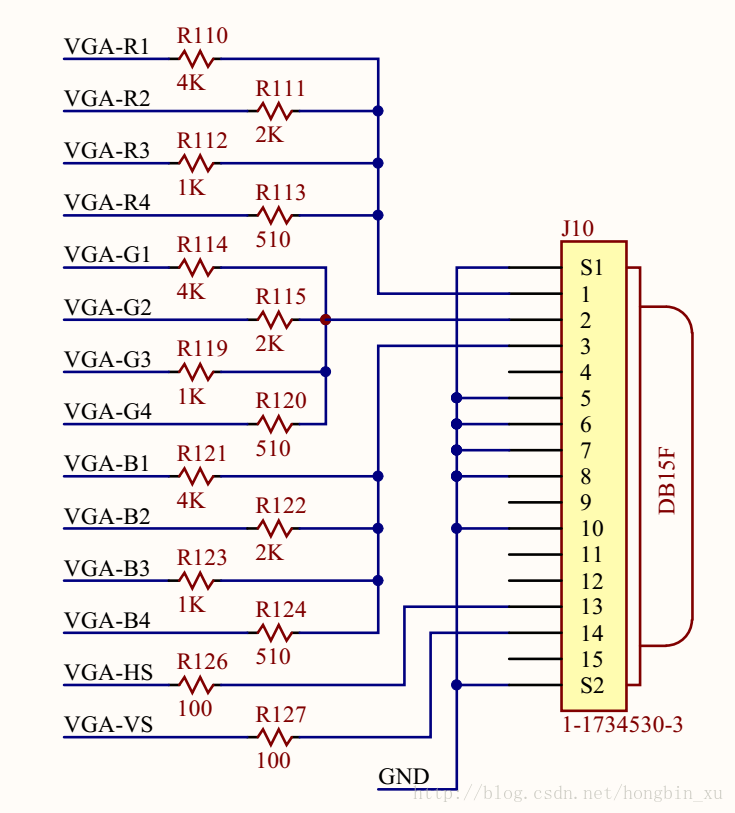

VGA硬件接口

到zedboard官方给出的原理图中查看:

RGB信号,各四位;这里的设计是使用了电阻分压模拟了DAC芯片实现了4X4X4的RGB信号,如果要更好的显示效果还是建议使用专门的DAC。

上面给出了所有的引脚分配。

VGA时序分析

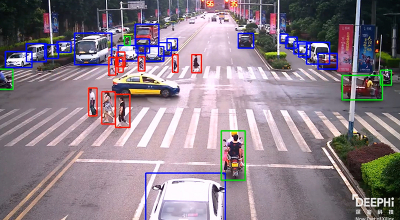

DeePhi 在 Xilinx FPGA 上使用 DeePhi 技术演示 SSD算法

在网上看了很多的介绍,基本都是一样的,但是根据这些博客,自己验证了下发现结果和matlab中不一样。

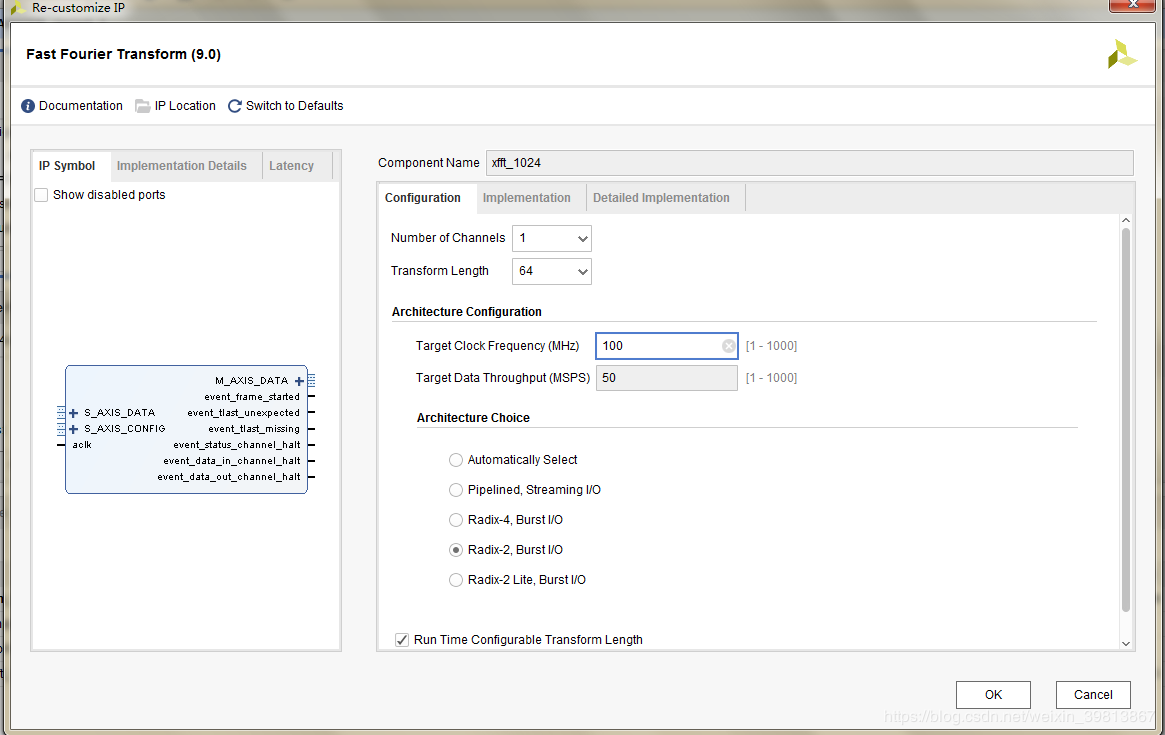

1.配置IP核

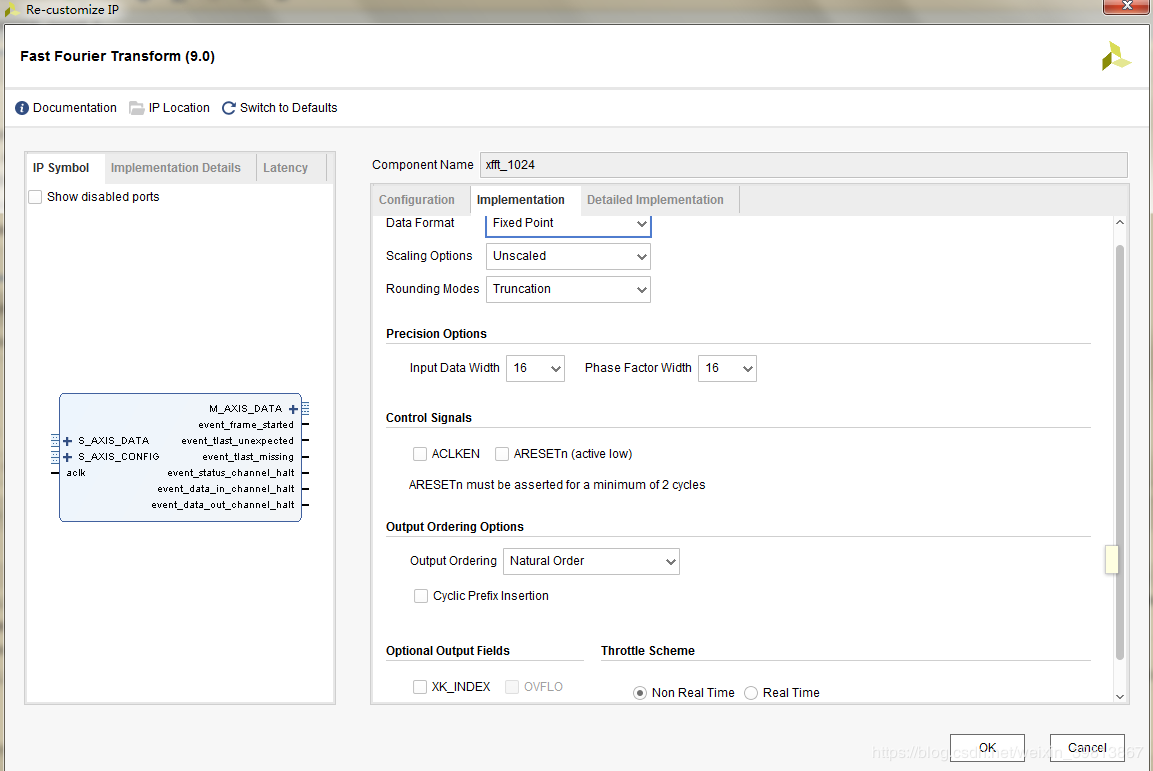

用vivado17.2 IP版本为9.0,配置首先配置最大长度为64,时钟为100MHz,将长度可以改变选中,如下图所示:

进一步的配置,设置数据为整型,未缩放,输入16bit,输出自然顺序(不然虚部不方便验证)。

第三页默认

据外媒报道,近期芯片公司发布的财报大多表现暗淡,而FPGA芯片巨头Xilinx成为了行业的亮点:5G网络的早期建设推动了该公司营收增长,时间上早于分析师预期,而势头上也要好于预期。5G网络的速度是现有网络的100倍,预计将为设备和芯片厂商带来数十亿美元的收入。

如果你已经有了一个设计并且想将这个设计移植到另一款目标器件上,这篇文章将帮助你确定这种转换所应遵循的步骤。这篇文章不会涉及与原设计完全不同的转换方式,从底层组件来看并非完全不同的。对于这种转换你应该遵循特定的转换指南,比如UltraScale系列转换为Versal系列器件,这篇文章的主题就是这种转换的方法,转换的方式通常是相似的。

AI 对 AI:在 FPGA 中为数据中心及端点自动生成深度神经网络加速器

在这篇文章中,我们将让这块开发板的 Cortex-A53 透过 AXIO_GPIO 模块,点亮板子上的 LED 灯,并且透过 ps_uart0 输出一些讯息。

本篇主要介绍MIPI物理层规范中的D-PHY,主要包括D-PHY的架构、操作模式、电气特性等。

在读取 IBERT 的自适应环路代码时,出现了与 DMONITOROUT 的期望值不同的值。

利用XilinxISE软件开发FPGA的基本流程包括代码输入、功能仿真、综合、综合后仿真、实现、布线后仿真与验证和下班调试等步骤。如下图所示