【视频】SDAccel 内核接口的硬件调试

judy 在 周一, 12/17/2018 - 17:29 提交

了解 SDAccel 提供的硬件调试功能,如何查看与内核之间的实时 AXI 传输,以及如何准备主机代码以使用 SDAccel 硬件调试功能。

了解 SDAccel 提供的硬件调试功能,如何查看与内核之间的实时 AXI 传输,以及如何准备主机代码以使用 SDAccel 硬件调试功能。

在逻辑电平互连的过程中,经常会出现电流倒灌的现象。本篇从IO口的结构出发,分析电流倒灌的原因及解决措施

市场研究公司 BCC Research 在 2018 年 9 月公布了最 新的《机器视觉技术全球市场报告》。报告中指出,由于 受到制药、食品和饮料以及汽车行业强劲需求的驱动,全球机器视觉技术市场在规模上已经达到了一个新高度。

在调试Vivado 过程中,由于生成的BIT文件过大,而我使用的FLASH又是32MBIT的,出现了FLASH过小,无法烧录的情况。网上搜索到的方法都是说“generate progamming file下会有一个属性,进去了在-g compress后面打勾”,但是我使用的是VIVADO2017.2,该版本根本找不到这个选项。于是只能自己慢慢摸索,终于,找到了两种方法

实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。

Skreens 展示了其系统解决方案,用于在 Xilinx FPGA 上开发加速视频和机器学习应用,和/或将加速视频处理集成到现有产品中。

被广泛应用于各种产品,具有开发时间短、成本效益高以及灵活的现场重配置与升级等诸多优点。很多新型FPGA利用先进的技术实现低功耗和高性能。他们通过新的制造工艺降低了内核电压,从而扩大电源电压范围并提高电流量。很多FPGA对每个电源轨的供电需求不尽相同

刚刚,斯坦福全球AI报告正式发布。今年的报告,从学术、工业、开源、政府等方面详细介绍了人工智能发展的现状,并且记录了计算机视觉、自然语言理解等领域的技术进展。

在ZedBoard上开发基于QNX操作系统PL部分UART设备驱动的过程中遇到了一点问题,问题原因不明但总结下来给大家提供参考,也以便以后对QNX的进一步了解后回顾这些问题。

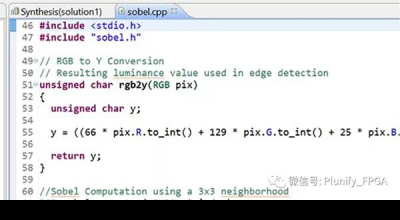

用软件从 C 转化来的 RTL 代码其实并不好理解。今天我们就来谈谈,如何在不改变 RTL 代码的情况下,提升设计性能。本项目所需应用与工具:赛灵思HLS、Plunify Cloud 以及 InTime。