【视频教程】Simulink:仿真与基于模型的设计

judy 在 周四, 08/09/2018 - 15:38 提交

Simulink 是一个面向多域仿真并和基于模型设计的框模块图环境。它支持系统级设计、仿真、自动代码生成以及嵌入式系统的连续测试和验证。在迁移到硬件之前,在 Simulink 中设计和仿真您的系统。探索和实现您原本不会考虑在内的设计 ,而无需编写 C、C++ 或 HDL 代码。

Simulink 是一个面向多域仿真并和基于模型设计的框模块图环境。它支持系统级设计、仿真、自动代码生成以及嵌入式系统的连续测试和验证。在迁移到硬件之前,在 Simulink 中设计和仿真您的系统。探索和实现您原本不会考虑在内的设计 ,而无需编写 C、C++ 或 HDL 代码。

作者:Paul S.Levy, 赛灵思功能安全系统高级工程师

产品编号:TAILMV2000SA-ES

供应商:S2C Incorporated

器件支持:Virtex-7

简介

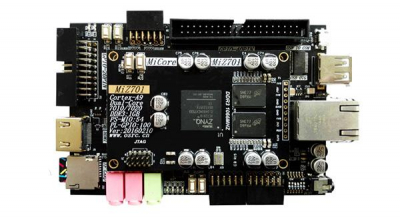

前段时间买了一块米联客的7010开发板,打算尝试为这块开发板搭建一个简单平台。

用户自定义开发板与SDSoc直接支持的开发板的区别在于,直接支持的开发板已经根据板子上的硬件完成了一系列重要配置(如时钟、DDR型号),所以在为用户开发板搭建平台时,只需要根据该开发板的硬件实际情况进行相应的配置即可。

1.定义

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

作者:周肇基/施天从/谢昆霖;新通讯 2018 年 8 月号 210 期《 技术前瞻 》

前言

PCIe 链路训练及稳定性问题形成了绝大多数互联互通问题。

本文档主要介绍在带集成工具的 Xilinx Vivado 设计套件中调试这些问题的使用案例。

本文档将重点介绍如何通过捕获在 UltraScale FPGA Gen3 集成块中用于 PCI Express 内核的链路训练调试信号来使用 Vivado ILA 进行调试。

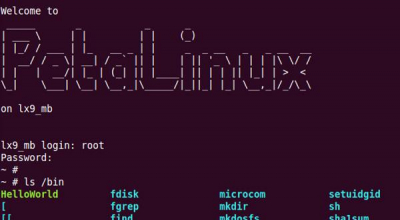

PetaLinux 工具提供在 Xilinx 处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件。理想适用于提升设计生产力,该解决方案与 Xilinx 硬件设计工具协同工作,为 Zynq® UltraScale+™ MPSoC、 Zynq®-7000 SoC、和 MicroBlaze™ 简化了 Linux 系统的开发。

本文是该系列的第8篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程;第7篇介绍了其中数据类型的选择与位宽截断的问题。本文将对其中使用到的Reinterpret和Convert模块进行详细介绍。