ZYNQ AXI GPIO中断实验——FPGA Vitis篇

judy 在 周四, 05/25/2023 - 09:44 提交

使用ZYNQ最大的疑问就是如何把PS和PL结合起来使用。本实验使用两个AXI GPIO的IP核

使用ZYNQ最大的疑问就是如何把PS和PL结合起来使用。本实验使用两个AXI GPIO的IP核

本篇博文主要讲解在 PL 中从 IP 核到 PS 之间需要完成含超 16 次中断的布线的情况下,该如何使用 AXI Interrupt Controller (INTC)

本章演示了如何利用 Vivado® 工具并使用 PL AXI GPIO 来创建嵌入式设计。其中还演示了如何在 Versal 器件上为基于 Arm® Cortex™-A72 核的 APU 配置并构建 Linux 操作系统。

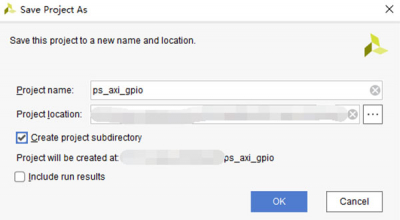

前面讲过如何用的是PS端的EMIO点亮PL端LED灯,但是并没有与PL端产生交互。本章介绍另外一种控制方法,在ZYNQ当中可以使用AXI GPIO,通过AXI总线控制PL端的LED灯。同时也介绍了PL端按键的使用。

本能篇主要讲一下AXI GPIO 中断,AXI GPIO 中断也是共享外设中断的一种。本讲和上一讲说的中断很像,区别就是AXI GPIO 中断需要AXI GPIO核。