Xilinx FPGA AXI4总线实例介绍(二):5 个读写通道

judy 在 周四, 03/25/2021 - 09:32 提交

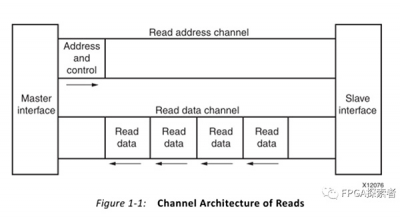

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间双向传输,且数据传输大小可以不同。AXI4中的限制是一个突发事务(Burst)最多可以传输256个数据,AXI4-Lite只允许每个事务传输1个数据。

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间双向传输,且数据传输大小可以不同。AXI4中的限制是一个突发事务(Burst)最多可以传输256个数据,AXI4-Lite只允许每个事务传输1个数据。

AMBA® AXI4(高级可扩展接口 4)是 ARM® 推出的第四代 AMBA 接口规范,AMBA(Advanced Microcontroller Bus Architecture)是片上总线标准,包含AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和 APB(Advanced Peripheral Bus)。

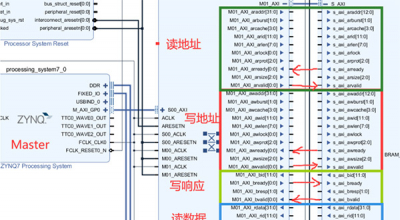

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口