FPGA vivado系统集成操作

judy 在 周三, 04/03/2019 - 11:37 提交

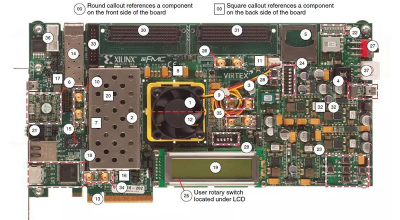

本文档系列是我在实践将简单的神经网络LeNet-5实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。本文档重点探讨vivado软件的使用。

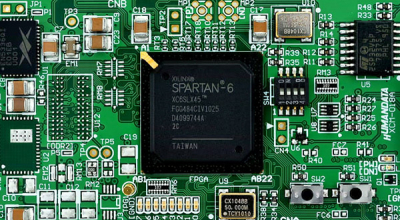

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

本文档系列是我在实践将简单的神经网络LeNet-5实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。本文档重点探讨vivado软件的使用。

利用卷积神经网络(Convolutional Neural Network, CNN) 等深层神经网络的解决方案,可以逐渐取代基于算法说明的传统图像处理工作。尽管图像预处理、后期处理和信号处理仍采用现有方法进行,但在图像分类应用中(缺陷、对象以及特征分类),深度学习变得愈加重要

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 答案应该与上面问题一致。同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变

针对CMOS图像传感器采集图像过程中的噪声预处理问题,提出一种在FPGA中实现的可配置的自适应加权均值滤波模块设计方案。该模块通过检测滤波窗口内不同方向的方差来确定纹理方向,从而自动生成相应的加权系数,可以对宽度不超过4 094像素的图像进行流水线式的加权均值滤波处理,达到去噪保边的目的

据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,HLS可以在一定程度上降低FPGA的入门门槛(不用编写RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构

近年来,现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)技术飞速发展,集成度越来越高,功耗、成本不断降低,特别是在并行处理、流水线设计、可重构等方面具有独一无二的优势,使其逐渐在雷达信号处理领域中占据重要地位。本文使用FPGA对距离徙动校正算法进行了硬件实现,具有实时性高,处理速度快,精度高等特点

在FPGA系统中有两个基本准则非常重要,分别为:数字表示法和代数运算的实现。本博文主要介绍数字表示。

本文档系列是我在实践将神经网络实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。本文档重点探讨如何与片上ARM进行连接通讯和控制。

随着FPGA在数据中心加速和Smart NIC在SDN和NFV领域的广泛应用,基于以太网接口的FPGA开发板越来越受到关注。而更高速率的以太网接口技术则是应用的关键,本文将详细介绍基于FPGA的10G以太网接口的原理及调试技术。

NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FPGA带来的低延迟和高数据吞吐量特性使得FPGA在工业、通信和汽车ADAS(高级驾驶辅助系统)等应用中得到广泛采用。汽车场景中摄像头系统的快速启动时间要求就是很好的一个例子——车辆启动后后视图像在仪表板显示屏上的显示速度是最为突出的设计挑战