【FPGA技巧篇】时钟设计技巧

judy 在 周一, 02/21/2022 - 10:15 提交

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有灵活性和可重配置性,可以根据特定应用的需求在现场进行编程和配置。与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA允许用户根据需要定制逻辑功能和连接,从而实现各种不同的数字电路设计。

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。

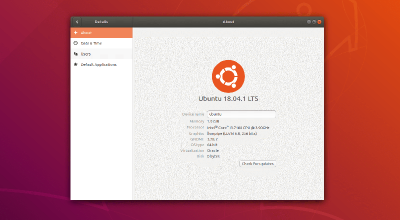

在Ubuntu 18.04下使用Vivado Jtag加载FPGA,发现找不到器件。

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错

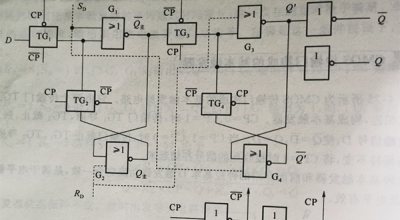

同步电路系统设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是FPGA设计的基础。但是伴随着集成电路的微缩化和大规模化,同步式电路的一些问题也显现出来。

在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个?

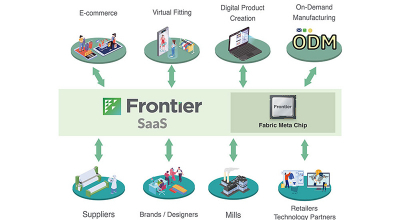

用户一键就可将数字布料快速转换成3D档案,再串接3D设计软件到电商橱窗,实现从工厂端到品牌设计、电商通路的服饰数字化生产流程

FPGA下游应用场景广泛,需求稳健增长,未来在5G、AI、数据中心、自动驾驶等高算力需求推动下,FPGA芯片市场需求量增长具确定性

在此次疫情防控中,AI、大数据、5G、云网络的运用可谓是“多点开花”。我们迫切的想要知道,在新冠“战役”的背后,FPGA发挥了什么作用?

一个完整的通信系统,是十分庞大的,没有几百上千人,在短时间内是做不好的。本文仅仅针对5G NR中的基带算法部分,做一个简单梳理。