Vivado BOOT.bin 文件生成

joycha 在 周四, 02/28/2019 - 10:04 提交

Vivado BOOT.bin 文件生成

Vivado BOOT.bin 文件生成

在Vivado中进行HDL代码设计,不仅需要描述数字逻辑电路中的常用功能,还要考虑如何发挥Xilinx器件的架构优势。目前常用的HDL语言有三种

本文将介绍Vivado提供的块级综合流程(Block Synthesis Flow),允许设计者将某些全局设置和策略应用于特定的层次结构中,且可以与设计中的其它模块不同。

Vivado综合工具支持直接在RTL文件或XDC文件中设置综合属性。如果Vivado识别出设置的属性,会创建与之相关的逻辑电路;如果不能识别设置的属性,会将该属性和值存放在生成的网表中。因为某些属性,比如LOC约束适用于布线过程,因此必须保留该属性配置情况

在HLS中使用帧间差分法生成了IP核,这里讲述如何在vivado中调用IP core

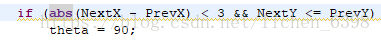

在viado SDK的程序开发中会出现以下的问题

出现问题的原因可能是

没有添加对应的头文件

解决办法:添加对应的头文件 如上图:添加#include”stdlib.h”

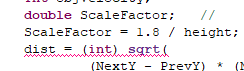

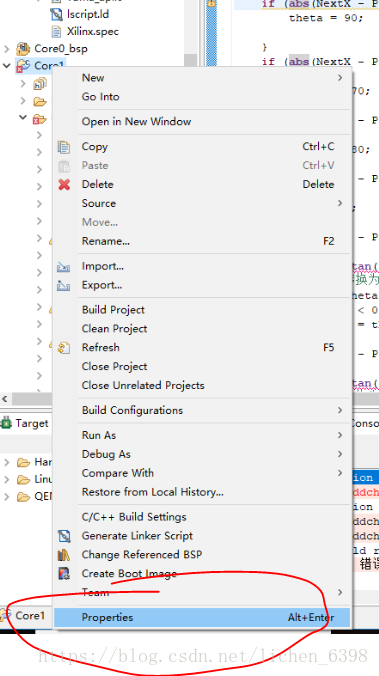

没有添加库函数

解决的方法是:

点击工程文件,右键,选择Properties

如下图:

选择 C/C++ Build 下的Setting 选择:Libraries 添加m文件 因为abs()位于math.h函数里

如何存储关键数据的方法,属于规模测试验证的手段,但对于Verilog的调试过程还不够直观,因为无法确切地了解Verilog代码仿真中各个关联信号是如何作用的。Verilog的确可以像C/C++一样启动调试模式,针对每行代码进行调试。但请注意,由于Verilog是并行执行的,而仿真是采用delta时间逐步并行推进的,采用代码调试较为困难,所以常常需要存储全部或部分仿真数据,这就是波形文件。

在调试Vivado 过程中,由于生成的BIT文件过大,而我使用的FLASH又是32MBIT的,出现了FLASH过小,无法烧录的情况。网上搜索到的方法都是说“generate progamming file下会有一个属性,进去了在-g compress后面打勾”,但是我使用的是VIVADO2017.2,该版本根本找不到这个选项。于是只能自己慢慢摸索,终于,找到了两种方法

一、在想要抓取的信号之前添加(* mark_debug = "true" *)、保存、编译。如:

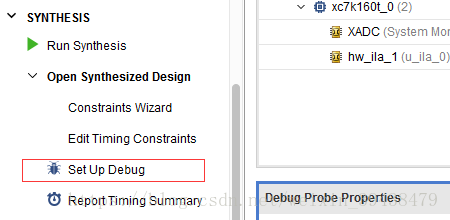

二、编译完成之后点击set up debug。

点击下一步.....

直至出现如下页面

一、如何在Vivado(2017.2)中添加自己喜爱的文本编辑器。

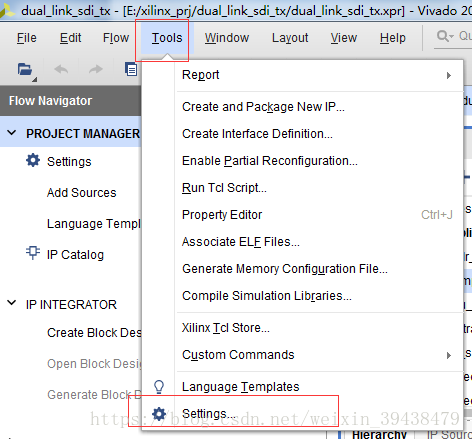

1、打开Vivado软件,选择Tools-->Settings。

2、在弹出的界面中选择Text Editor-->Custom Editor。

3、在Editor:框中输入你想要添加的文本编辑器的路径。注意:后面需添加[file name] -[line number]。