Vitis HLS 系列 1:Vivado IP 流程(Vitis 传统 IDE)

judy 在 周三, 04/30/2025 - 13:16 提交

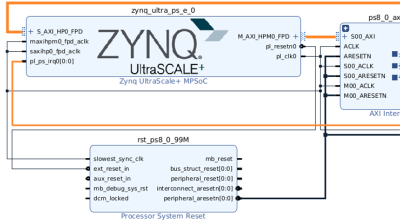

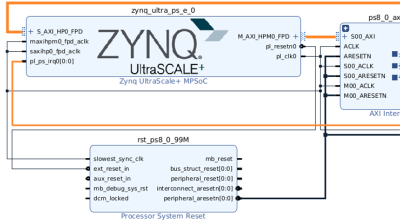

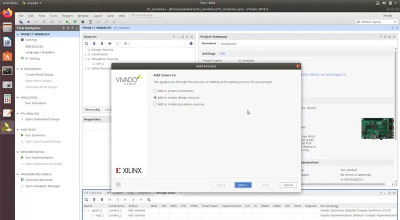

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器

根据UG973选择Vivado2024.2版本选择匹配的VCS版本和One Spin,这里Vivado 2024.2 匹配的 OneSpin 360版本是OneSpin 360 (2023.2)和Red Hat 64/ SUSE Linux/ Windows 10 64-bit。

了解 AMD Versal 产品组合与前几代 FPGA 相比在时钟架构功能的增强,并了解如何利用 AMD Vivado™ 工具的先进功能快速完成设计并实现性能目标。

在 24.2 版本中,GT Wizard 迎来了重要的更新,添加了新的IP: GT Wizard 子系统。旨在为用户带来更高的灵活性和兼容性。本博客将介绍 GT Wizard 子系统的使用方式。

AMD Vivado™ Design Suite 实现突破性优化,可显著加快 Versal™ 自适应 SoC 硬件设计工作,与此同时大大简化了从旧架构到新架构的迁移

习惯了用linux下emacs写代码,最近换到了windows下开发fpga,也想用emacs,怎么办呢?原来在Vivado IDE里就可以设置,但也有一些注意事项。

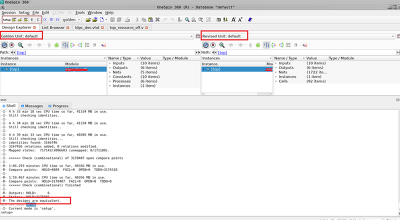

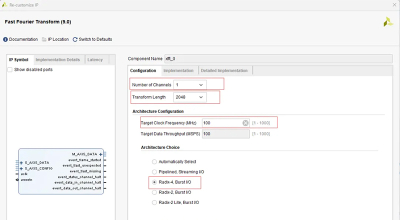

今天分享一下vivado FFT IP,包括配置要点以及使用难点,让读者快速上手。

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题,不知道大家有没有遇到,就是新设计的自定义 RTL 文件无法快速的添加到Block Design中

本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计