作者:Rachel Gaines,AMD工程师;来源:AMD开发者社区

这篇博客旨在逐步演示如何使用 Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着,您将在 Vivado 设计中使用此 HLS IP,并使用嵌入式 Vitis 应用控制此 HLS IP。

具体的运行和测试条件如下:

操作系统:Ubuntu 20.04

版本:2023.1

**注释**:请确保使用您的操作系统支持的版本 - 受支持的操作系统

这篇博客使用的工具流程为 Vitis HLS > Vivado > Vitis IDE。我们将使用 Vitis HLS 创建一个自定义 IP,将该 HLS IP 合并到 Vivado 的硬件设计中,然后创建一个与 HLS IP 通信的 Vitis 应用。该 Vitis 应用将按照自定义硬件上的嵌入式工程所需进行设置。应用代码将利用自动生成的 HLS API 驱动程序调用来控制 HLS IP 并与之通信。整个流程假设您已经安装了 Vitis、Vitis HLS 和 Vivado。

这篇博客的底部有一个可下载的 ZIP 文件,其中包含脚本和源代码,以供参考和/或重新创建设计。

第 1 步 - 下载并解压缩 referenceDocs 文件夹

该文件夹保存在所需工作位置。vitis_hls 和 vivado 各有单独的文件夹。稍后,您可以创建自己的 Vitis 应用工程文件夹。

第 2 步 - 创建 HLS IP

打开 Linux 终端,执行以下命令以便:

进入 vitis_hls 文件夹 - 该文件夹包含 HLS IP 的源代码。

运行 TCL 脚本来设置 HLS 工程 - 该脚本还将运行 C 语言仿真、C 语言综合与协同仿真。

在 GUI 中打开 HLS 工程

cd vitis_hls vitis_hls -f run_hls.tcl vitis_hls -p proj_axi_master

打开 GUI 后,检查 example.cpp 源代码。HLS IP 使用 volatile 指针和 memcpy 函数在存储器上读取和写入数据。memcpy 需要一个缓冲器来存储存储器传输事务的各项结果。m_axi 接口编译指示要求此 IP 使用存储器映射。深度设置为 50 意味着串流在给定时间最多可以容纳 50 个未完成的元素,选择该值是为了匹配缓冲器的大小。s_axilite 接口编译指示允许此 IP 接受应用的控制,并与 Zynq 器件通信。

您可使用 GUI 左下角的 Flow Navigator,以便在 GUI 中运行 C 语言仿真、C 语言综合与协同仿真,查看每项报告并熟悉 IDE。当您准备就绪后,可以通过在 Flow Navigator 中选择“Export RTL”(导出 RTL)来导出 HLS IP,以便在 Vivado 中使用。

第 3 步 - 创建 Vivado 平台

有两种方法可用于创建 Vivado 平台。

选项 1:

使用以下所示命令从“vivado”文件夹运行 Tcl 脚本。运行此脚本后,将创建一个 Vivado 工程,随后您可在 GUI 中打开该工程。在 GUI 中,您需要综合、实现、生成比特流,并导出硬件。

vivado -mode tcl source hlsPlatformDesign.tcl

您的另一项选择是按照以下步骤在 Vivado 中自行创建平台:

打开 Vivado,并使用 ZCU102 评估板创建一个新工程

将 Vitis HLS IP 添加到 IP 目录中

打开 IP 目录,右键单击并选择“add Repo”(添加仓库)

浏览到导出 IP 的位置,并将“ip”文件夹添加到目录中。默认路径为 <pathToProject>/solution1/impl/IP。

注释:如果希望使用不同的位置将 HLS IP 添加到 IP 目录中,可以使用导出 HLS IP 时创建的 export.zip 文件。它位于相同的默认路径中,但您可以将其移至期望的位置,并使用该位置代替“ip”文件夹,以添加到 IP 目录中。“ip”文件夹所含内容与解压后 IP 的内容相同。

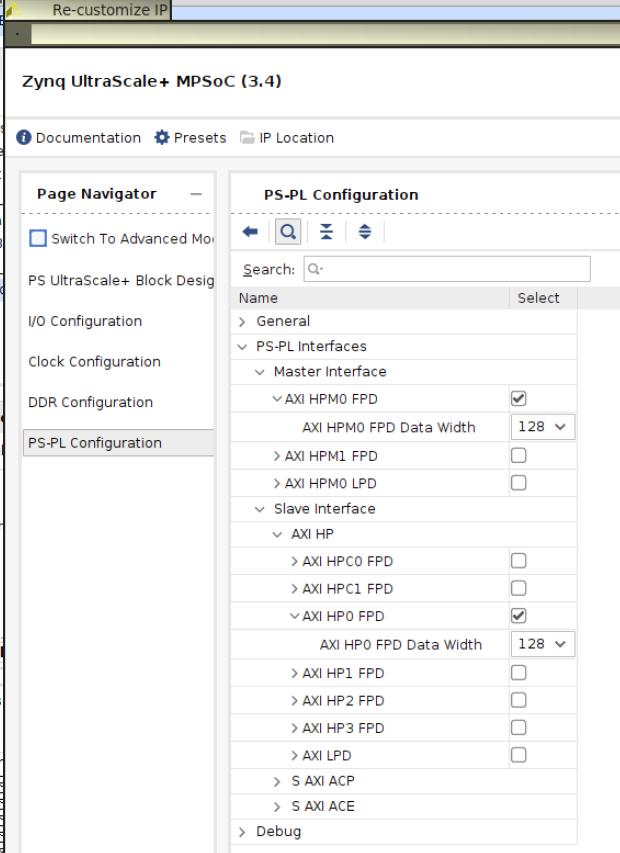

创建一个新的块设计,并添加 HLS IP 和 Zynq UltraScale+ MPSoC。通过双击 Zynq,对其进行自定义。在该设计中,我们添加了 S_AXI_HP0_FPD 端口。该评估板默认启用 DDR,但请在“DDR Configurations”(DDR 配置)选项卡中确认 DDR 是否已启用。

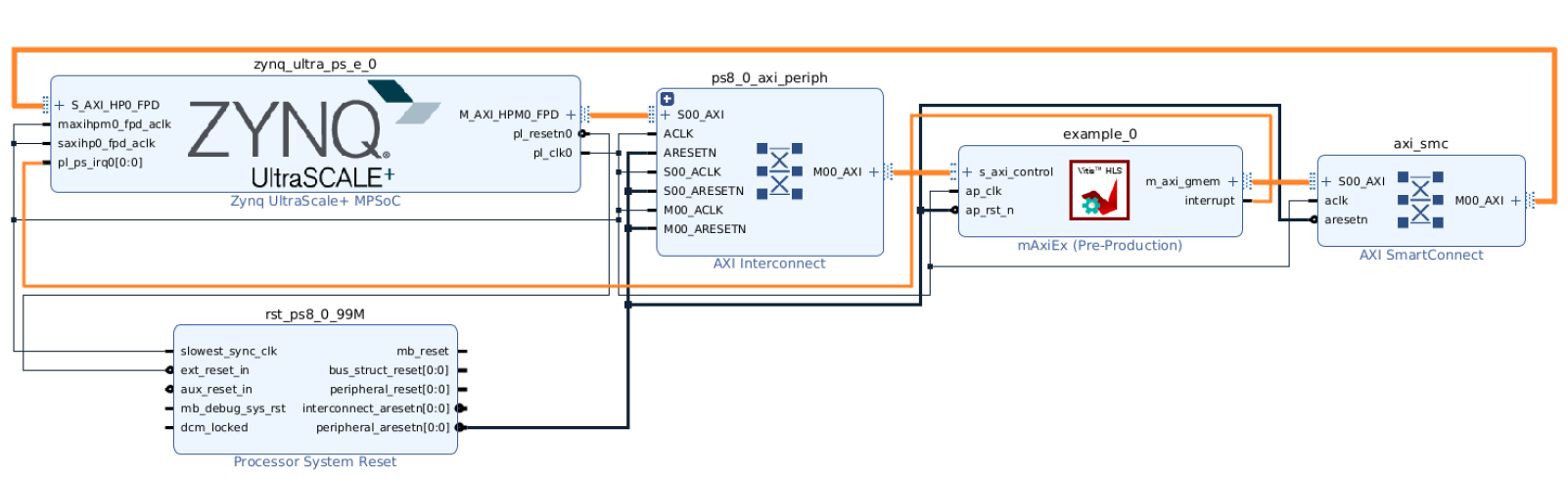

使用设计辅助来运行自动连接。它将通过 AXI Interconnect 和 AXI SmartConnect 自动连接 Zynq 和 HLS IP。

您必须手动将 HLS IP 上的中断端口连接到 Zynq 上的 pl_ps_irq 端口。您的设计应与以下截屏相似:

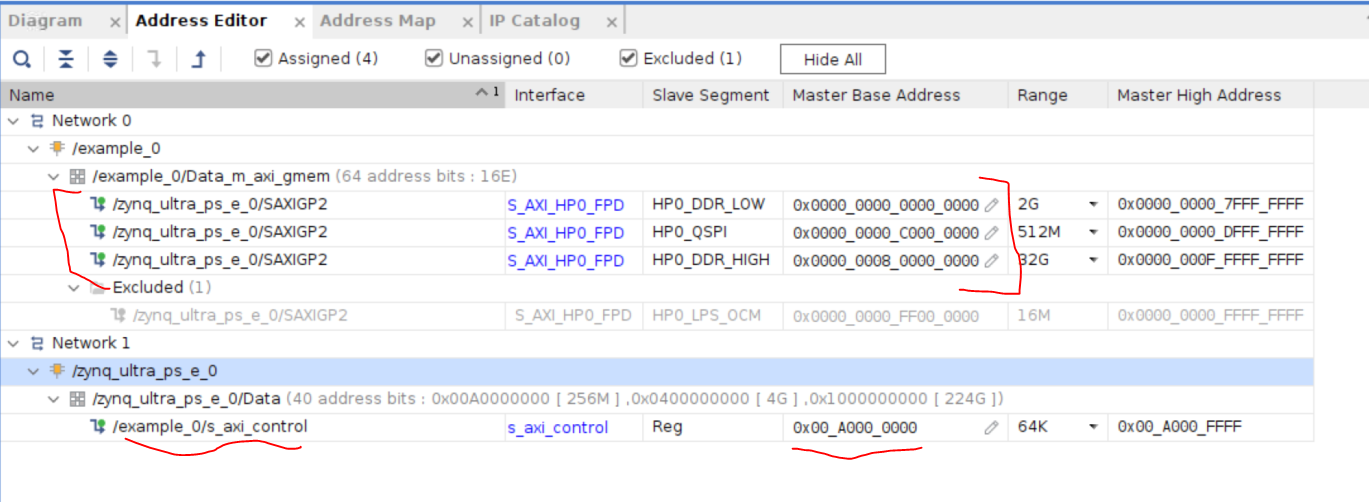

打开“Address Editor”(地址编辑器)选项卡,确保已如下所示分配了所有地址。

确认该设计。如果没有错误,则运行综合、实现和生成比特流的步骤。完成后,选择“File > Export > Export Hardware”(文件 > 导出 > 导出硬件)导出设计,并将 XSA 文件保存到期望的位置。注释:在导出硬件时,确保选择“Include bitstream”(包含比特流)。

第 4 步 - 创建 Vitis 应用

打开 Vitis 并选择“Create Application Project”(创建应用工程)- 这适用于独立的嵌入式系统

对于平台选择,请选择“Create a new platform from hardware (XSA)”(基于硬件创建新平台 (XSA))选项卡,并浏览到您在上一节中创建的 XSA 文件所在位置。单击“Next”(下一步)。

确保选中“Generate boot components”(生成启动组件)以及“psu_cortexa53_0”。在下一个框中按需更改平台名称,然后单击“Next”。

命名您的应用工程。系统名称将使用相同的标题。选择处理器“psu_cortexa53_0”。单击“Next”。

对于“Domain”(域)选择,请确保操作系统设置为“standalone”(独立),且架构为 64 位。单击“Next”。

对于模板,请选择“Empty C Application”(空的 C 语言应用)

设置源代码

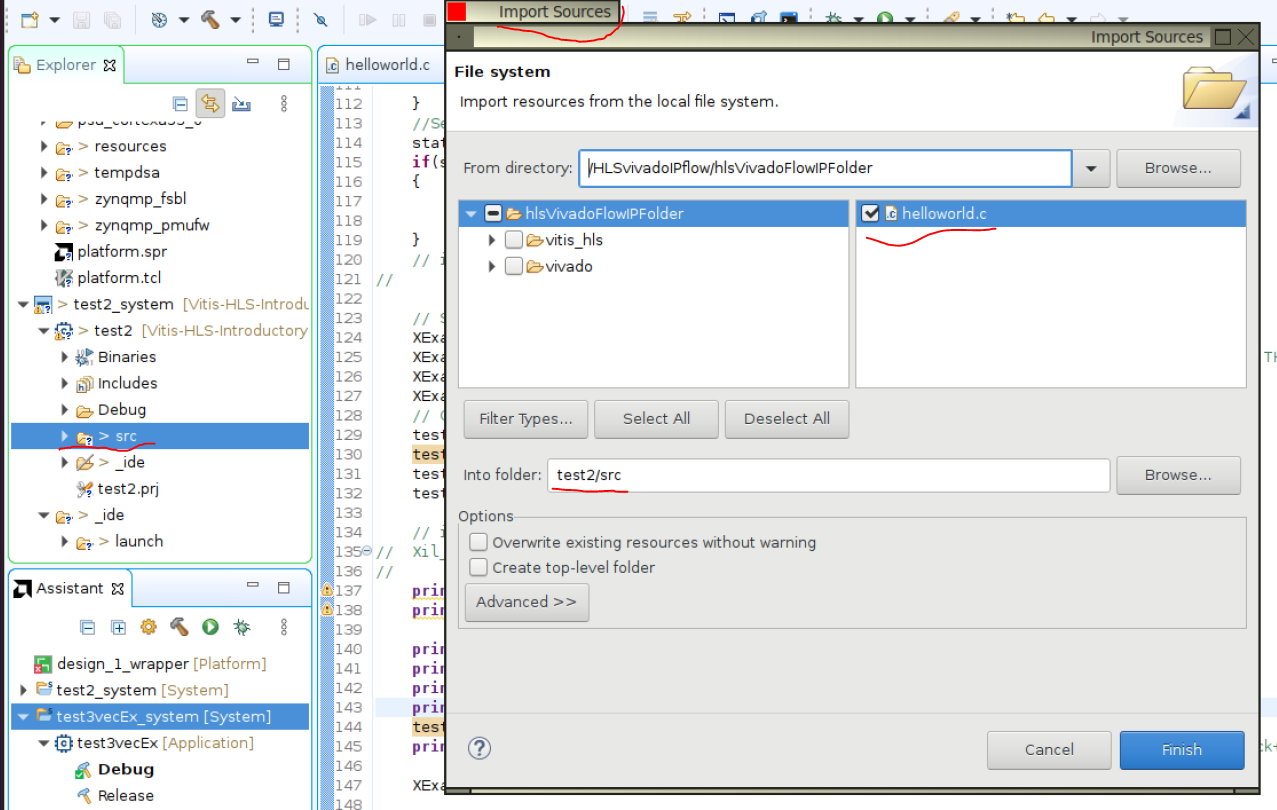

在 GUI 中打开 Vitis 工程后,在左侧的“Explorer”(资源管理器)选项卡中右键单击 projectName_system/projectName/src,然后选择“Import Sources”(导入源文件)。在弹出窗口中,浏览至源代码所在的文件夹。

添加 helloworld.c,它位于本博客随附的 ZIP 文件夹中,然后从文件列表中选择 helloworld.c,如下图所示。接着单击“Finish”(完成)。

检查 helloworld.c。整个过程中都有注释用于解释每一节的作用。以“XExample”开头的数据类型和函数调用是自动生成的 API 调用,用来控制 HLS IP 并与之通信。

关键要点包括:您必须创建一个 Vitis HLS IP 实例,如第 14 行所示,并使用 API 调用来获取/设置 IP 与数据并且启动它(第 34、35 和 48 行)。

您还必须完成另一项不寻常的操作,即,使用 Xil_DCacheInvalidate() 函数,告诉处理器对 DDR(而非其高速缓存)执行读取/写入操作,以确保处理器和 HLS IP 在相同的位置执行读取/写入。

构建并运行工程

构建系统工程。这将构建整个工程,包括平台和应用。您可以右键单击系统工程或选择锤子图标。您还可以使用左下角的应用助手来构建和运行设计。

该工程未经软件仿真测试,因为这需要执行额外的步骤,不在本博客的讨论范围之内。但在 ZCU102 评估板上,已通过选择“Run As”(运行方式)选项中的“Launch Hardware”(启动硬件)来对该工程进行了测试和验证。当连接到该评估板时,您还可以运行调试器并单步执行代码。您可使用终端连接到 UART (com0),以查看硬件上的输出。

这篇博客的参考文件:

HLS - Tcl 脚本 - run_hls.tcl

HLS - 源代码 - example.cpp 和测试激励文件

Vivado - 从 write_project_tcl 创建的 Tcl 脚本

Vitis - 应用源代码