本文档涵盖了如何驱动 AMD Vivado™ Design Suite 来分析和改善您的设计,其中详解了下列主题:

使用 Vivado 集成设计环境 (IDE) 来查看消息、设计网表和交叉探测

方法论和 DRC 豁免

分析时序报告

生成所有网表、时序和设计收敛报告

智能设计运行、QoR 建议和 ML 策略

AMD 自适应计算文档按一组标准设计进程进行组织,以便帮助您查找当前开发任务相关的内容。您可以在设计中心页面上访问 AMD Versal™ 自适应 SoC 设计进程。您还可以使用设计流程助手来更深入了解设计流程,并找到特定于预期设计需求的内容。本文档涵盖了以下设计进程:

硬件、IP 和平台开发:为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado™ 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。

由于篇幅有限,本文仅选取部分内容进行分享。如果您希望获取完整版用户指南,请至文末点击链接进行下载。

IDE 中的交互设计分析

以下章节提供了 AMD Vivado™ Design Suite IDE 中的设计分析简介。IDE 与依赖工程模式的用户密切相关,但其中许多功能特性也适用于依赖非工程模式的用户。本章涵盖了下列技巧:

使用“Design Runs”(设计运行)窗口进行快速分析

在不同窗口之间进行交叉探测

方法论分析

布局布线分析

使用“Design Runs”窗口

“Design Runs”(设计运行)窗口是很实用的分析起点。它可显示当前运行状态。如需了解更多信息,请参阅《Vivado Design Suite 用户指南:使用 Vivado IDE》(UG893) 中的“使用‘Schematic’窗口”。

“Design Runs”窗口显示运行状态:“running”(正在运行)、“finished cleanly”(无错完成)或“finished with errors”(已完成但有错误)。

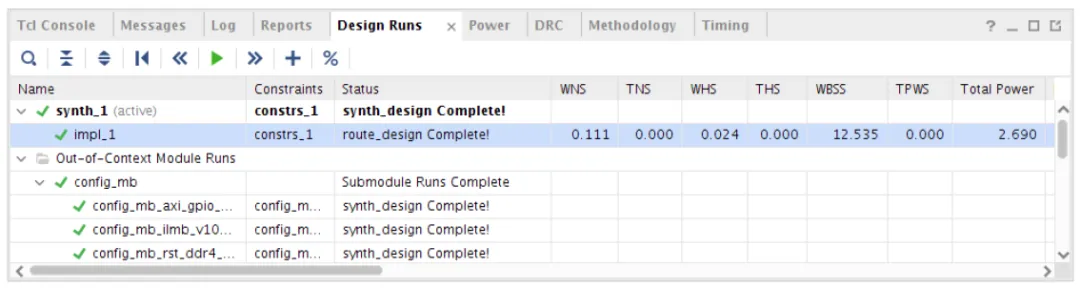

图 1:“Design Runs”窗口

“Design Runs”窗口列显示如下内容:

运行名称。

目标部件。

与运行关联的约束集。

运行策略。

运行的最后完成步骤的状态。

运行进度。

运行的开始时间。

执行过程中运行的耗用时间或已完成的运行的最终运行时间。

运行的时序评分:WNS、TNS、WHS、THS、WBSS 和 TPWS(如需了解有关这些数值的更多信息,请参阅 Report Timing Summary)。您可在此快速验证运行是否满足时序要求。如果未能满足时序要求,您必须使用“Timing Summary”(时序汇总)报告启动分析。

注释:WBSS 表示 report_bus_skew 报告的“Worst Bus Skew Slack”(最差总线偏差时序裕量)。

未能成功布线的信号线数量。

设计 LUT、FF、块 RAM、DSP 以及(如果适用)UltraRAM 的使用率。

总功耗估算。

运行策略简介。

方法论检查违例。

可用的 QoR 建议。

设计运行的增量模式。

选择运行时,右键单击菜单允许执行各项操作,例如,打开运行以便进一步分析,设置运行功能特性(如增量编译或 QoR 建议)。

获取完整版用户指南

请扫描二维码进行下载