AMD芯片定制,向第三方Chiplet打开大门

judy 在 周四, 06/16/2022 - 11:24 提交

随着 AMD 起航以制造更符合客户喜好的产品,AMD打开了芯片新大门。详细介绍了模块化芯片的未来,客户可以在定制芯片封装中混合和匹配非 AMD 处理器。

随着 AMD 起航以制造更符合客户喜好的产品,AMD打开了芯片新大门。详细介绍了模块化芯片的未来,客户可以在定制芯片封装中混合和匹配非 AMD 处理器。

FPGA与STM32等嵌入式开发最大的一个优点就是,可以在时序仿真阶段验证超过90%的功能,发现90%的问题

本视频介绍了此版本中的新功能和增强功能,包括 Versal® 设计的结果质量 (QoR) 改进、基于 ML 的资源估计、面向 Versal 器件的 ML 策略运行以及其他器件支持。

在Zynq MPSoC的器件里,PS (Processing System )集成了三个看门狗,分别是CSU SWDT,LPD SWDT和FPD SWDT。CSU SWDT用于保护CSU与PMU及其相关连接。

多路选择器MUX是一个多输入、单输出的组合逻辑电路,一个n输入的多路选择器就是一个n路的数字开关,可以根据通道选择控制信号的不同

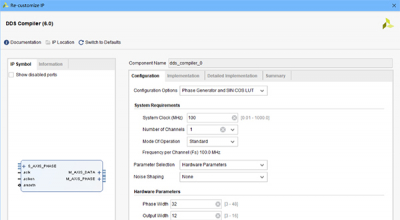

随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

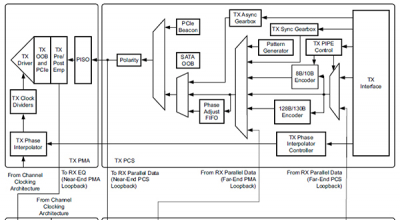

长时间没有做高速相关的FPGA单板开发,一直停留在GTX和GTP的时代,是时候梳理一下,从Xilinx的7系列到目前的ultrascale系列

您将学习如何简单地下载并创建Vivado工程,实现ADC EV12AQ600/605的串行接口,并缩短您的开发时间。

当我们使用Verilog时,对于信号定义为reg型还是wire型比较混乱,那么今天我们就来讲一讲如何快速的进行信号定义。

本文主要针对Xilinx SelectIO IP的GUI(图形用户界面),对每个参数进行详细解释,理解其中的内涵,快速完成驱动设计。