Xilinx 2020.1 MIG核读写DDR3内存,新建工程时配置MIG核的完整步骤

guanxiao_505740 在 周二, 08/31/2021 - 10:54 提交

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。

了解Versal™ ACAP的系统级优势以及与基于可编程逻辑的竞争器件的比较性能。

现场可编程门阵列(FPGA)的功能逐年扩展,始终围绕着一个核心价值,那就是较其他嵌入式技术的灵活性与性能优势。毫无疑问,近年来FPGA最主流的趋势是整合嵌入式处理器和接口设备,让设计人员能够将合适的任务分配给合适的运算引擎。

利用ROS 2来实现FPGA的软件定义硬件。

在Vitis下运行DNNDK例程时,(例程地址https://github.com/Xilinx/Vitis-In-Depth-Tutorial/blob/2020.1/Vitis_Plat...)运行到编译时,(20 Right click the hello_dpu project folder and select Build Project)一直出如下错误

Dialog半导体公司今天宣布扩大与赛灵思公司的合作。Dialog已获青睐为赛灵思的新型Kria自适应系统模块(SOM)提供电源管理方案,该模块面向智慧城市和智慧工厂中的视觉人工智能(AI)应用。

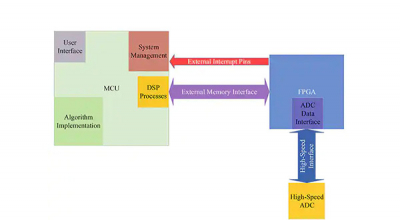

本文重点介绍分立式微控制器 (MCU) 和分立式现场可编程门阵列 (FPGA) 的组合,展示了这种架构如何适合高效和迭代的设计过程。利用研究资料、实证结果和案例研究,探讨这种架构的好处,并提供示范性的应用。读完本文,嵌入式系统设计者将对何时以及如何实现这种多功能硬件架构有个更好的理解

BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

Vitis统一软件平台将Xilinx各种软件统一,即支持Vitis嵌入式软件开发流程,又支持Vitis应用软件加速开发流程。本文介绍Vitis嵌入式软件中的linux应用程序开发流程。